## MC56F8006 Reference Manual

16-Bit Digital Signal Controllers (DSC)

MC56F8006RM Rev. 0 03/2009

## Chapter 1 Device Overview

| 1.1 | The MC56F8006 Series                                            | 1-1  |

|-----|-----------------------------------------------------------------|------|

|     | 1.1.1 Introduction                                              | 1-1  |

|     | 1.1.2 MC56F8006 Series Device Comparison                        |      |

| 1.2 | MC56F8006 Series Block Diagram                                  |      |

| 1.3 | High Performance Core                                           |      |

| 1.4 | Operation Range                                                 |      |

| 1.5 | Memory Configuration                                            |      |

| 1.6 | Module Configuration                                            |      |

| 1.7 | System Clock Generation and Distribution                        |      |

| 1.7 | 1.7.1 Clock Generation                                          |      |

|     | 1.7.2 Clock Distribution                                        |      |

|     | 1.7.3 Communication Between Peripherals                         |      |

|     | 1.7.4 Key DSC Attributes                                        |      |

|     | 1.7.5 Advantages of DSC                                         |      |

|     | 1.7.5 Advantages of DSC                                         | 1-14 |

|     | Chapter 2                                                       |      |

|     | Analog-to-Digital Converter (ADC)                               |      |

| 0.4 | • • • • • • • • • • • • • • • • • • • •                         | 0.4  |

| 2.1 | Introduction                                                    |      |

|     | 2.1.1 Features                                                  |      |

|     | 2.1.2 Related Material                                          |      |

|     | 2.1.3 Block Diagram                                             |      |

| 2.2 | External Signal Description                                     |      |

|     | 2.2.1 Analog Channel Inputs (ADn)                               |      |

| 2.3 | Register Definition                                             | 2-3  |

|     | 2.3.1 Status and Control Register 1A and 1B (ADC0_ADCSC1A and   |      |

|     | ADC0_ADCSC1B)                                                   | 2-3  |

|     | 2.3.2 Status and Control Register 2 (ADC0_ADCSC2)               |      |

|     | 2.3.3 Data Result Registers A and B (ADC0_ADCRA and ADC0_ADCRB) |      |

|     | 2.3.4 Configuration Register (ADC0_ADCCFG)                      |      |

| 2.4 | Functional Description                                          |      |

|     | 2.4.1 Clock Select and Divide Control                           |      |

|     | 2.4.2 Hardware Trigger                                          |      |

|     | 2.4.3 Conversion Control                                        |      |

|     | 2.4.4 Temperature Sensor                                        |      |

|     | 2.4.5 DSC Core Wait Mode Operation                              |      |

|     | 2.4.6 DSC Core LPstop Mode Operation                            |      |

|     | 2.4.7 DSC Partial Power Down Mode Operation                     | 2-12 |

| 2.5 | Initialization Information                                      |      |

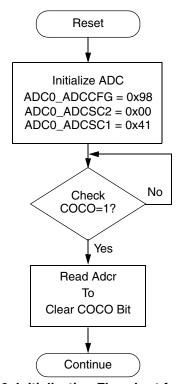

|     | 2.5.1 ADC Module Initialization Example                         | 2-13 |

| 2.6 | Application Information                                         | 2-15 |

|     | 2.6.1 External Pins and Routing                                 | 2-15 |

|     | 2.6.2 Sources of Error                                          | 2-16 |

|     |                                                                 |      |

# Chapter 3 Programmable Gain Amplifier (PGA)

| 3.1  | Introduction                                      |       |

|------|---------------------------------------------------|-------|

| 3.2  |                                                   |       |

|      | Definitions                                       |       |

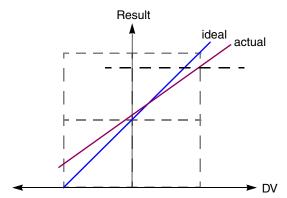

| 3.3  | Transfer Function                                 |       |

| 3.4  | Options for On-Chip Analog Conversions            |       |

| 3.5  | PGA Prerequisites                                 |       |

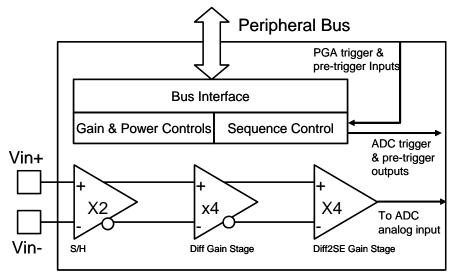

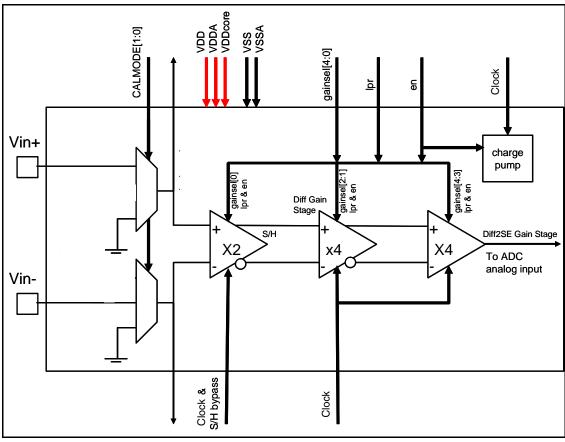

| 3.6  | Analog Block Diagram                              |       |

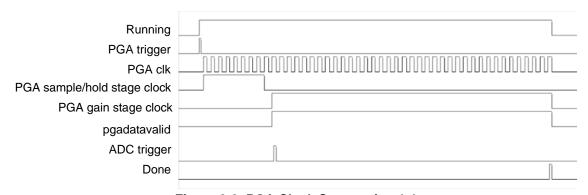

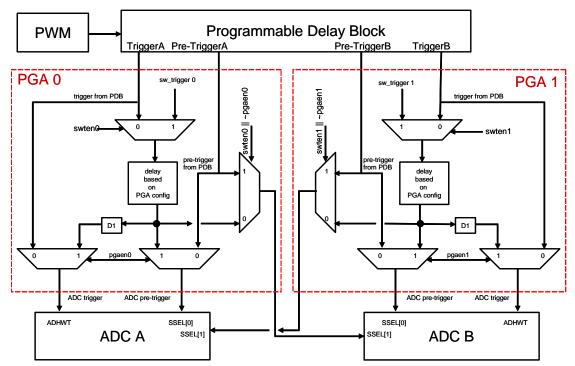

| 3.7  | Dual PGA Options                                  |       |

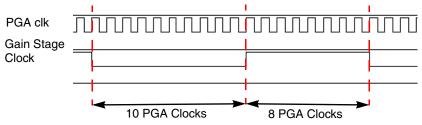

| 3.8  | PGA Clocking                                      |       |

| 3.9  | Effects on ADC Latency                            |       |

|      | ADC Triggers                                      |       |

| 3.11 | Modes of Operation                                |       |

|      | 3.11.1 PGA Power Down                             |       |

|      | 3.11.2 PGA Startup                                |       |

|      | 3.11.3 PGA Calibration                            |       |

|      | 3.11.4 PGA Mission Mode                           |       |

| 3.12 | Operation in Various Chip Operating Modes         |       |

|      | 3.12.1 Power Modes                                |       |

|      | 3.12.2 Operation During Run, Wait, and Stop       |       |

|      | 3.12.3 Operation During LPRun, LPWait, and LPStop |       |

|      | 3.12.4 Operation During Partial Power Down (PPD)  |       |

|      | Interrupts                                        |       |

|      | Reset Considerations                              |       |

| 3.15 | Register Definitions                              |       |

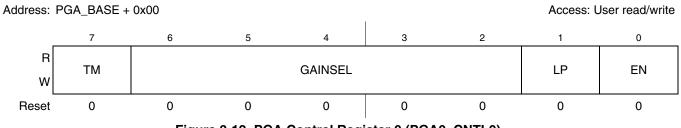

|      | 3.15.1 Control Register 0 (PGA0_CNTL0)            |       |

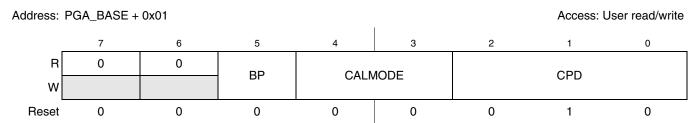

|      | 3.15.2 Control Register 1 (PGA0_CNTL1)            |       |

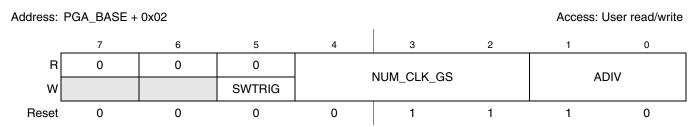

|      | 3.15.3 Control Register 2 (PGA0_CNTL2)            |       |

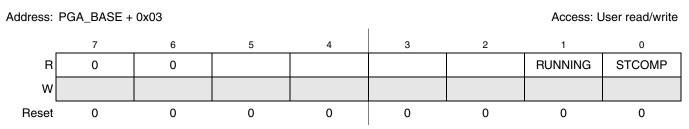

|      | 3.15.4 Status Register (PGA0_STS)                 | 3-19  |

|      | Chapter 4                                         |       |

|      | High Speed Comparator (HSCMP)                     |       |

| 4.1  | Introduction                                      | . 4-1 |

| 4.2  | Features                                          | . 4-1 |

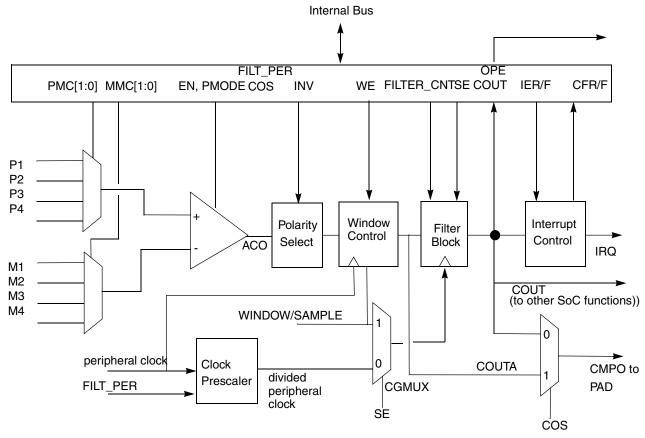

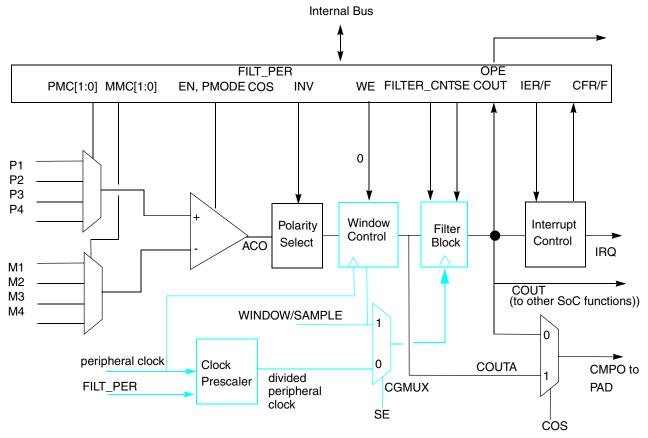

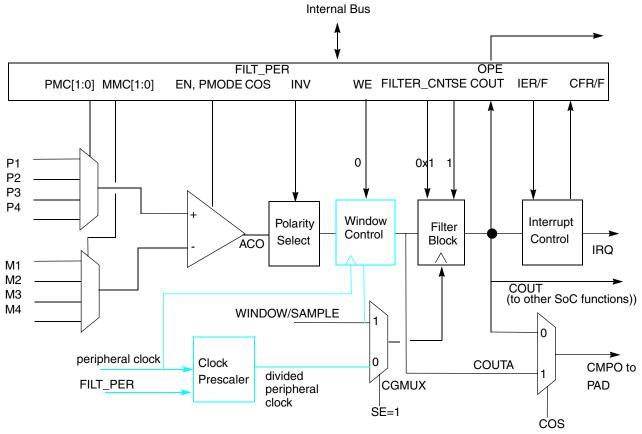

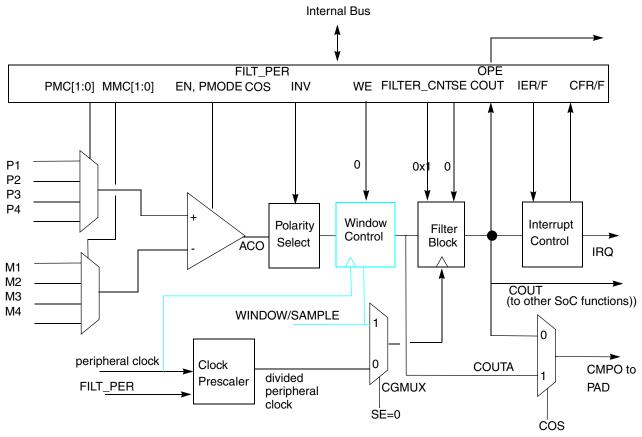

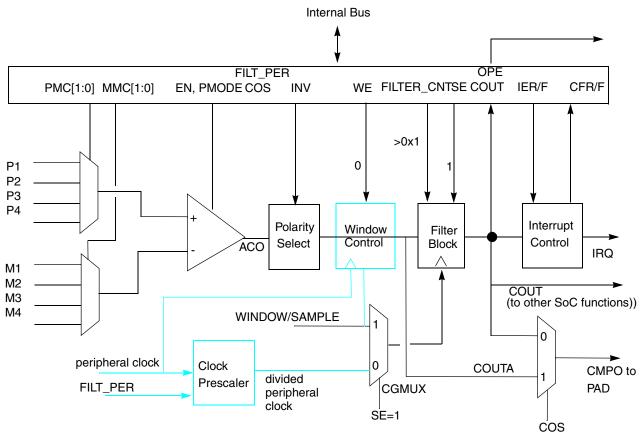

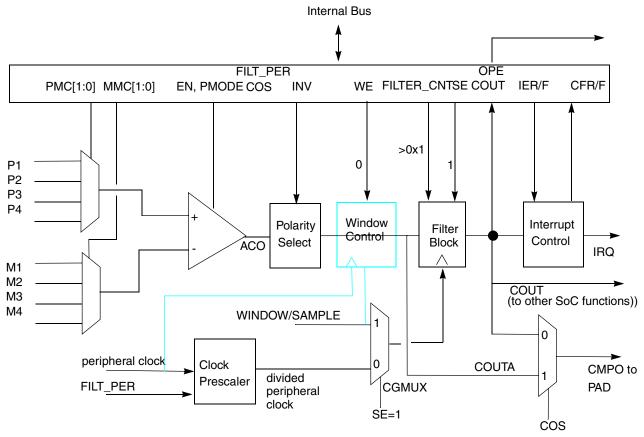

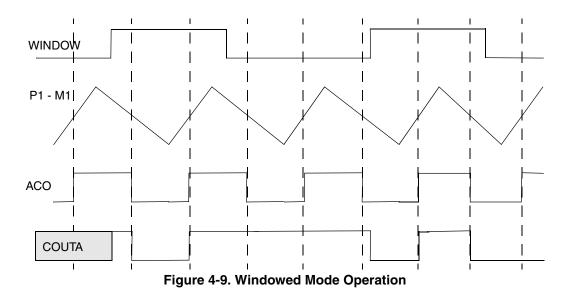

| 4.3  | Block Diagram                                     | . 4-1 |

| 4.4  | Pin Descriptions                                  | . 4-3 |

|      | 4.4.1 External Pins                               | . 4-3 |

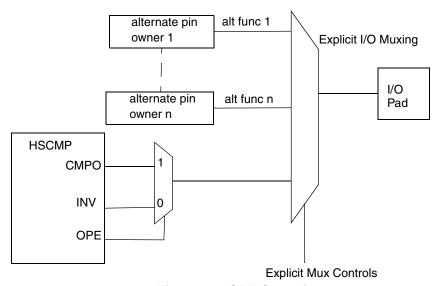

| 4.5  | Functional Description                            | . 4-3 |

|      | 4.5.1 HSCMP Functional Modes                      | . 4-4 |

|      | 4.5.2 Power Modes                                 |       |

|      | 4.5.3 Hysteresis                                  |       |

|      | 4.5.4 Startup and Operation                       |       |

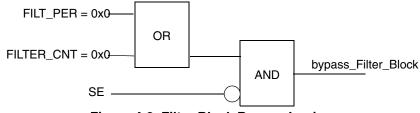

|      | 4.5.5 Low Pass Filter                             |       |

|      |                                                   | _     |

| 4.6        | Interrupts                                                                                                                 |

|------------|----------------------------------------------------------------------------------------------------------------------------|

| 4.7        | Memory Map and Register Definition                                                                                         |

|            | 4.7.1 Control Register 0 (CMP0_CR0)                                                                                        |

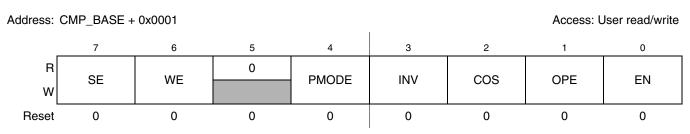

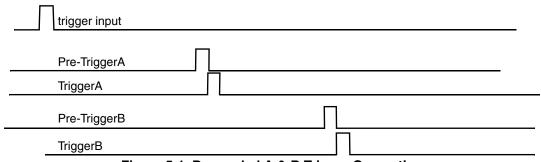

|            | 4.7.2 Control Register 1 (CMP0_CR1)                                                                                        |

|            | 4.7.3 Filter Period Register (CMP0_FPR)                                                                                    |

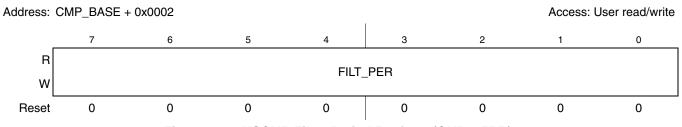

|            | 4.7.4 Status and Control Register (CMP0_SCR)                                                                               |

|            | <b>3</b>                                                                                                                   |

|            | Chapter 5                                                                                                                  |

|            | Programmable Delay Block (PDB)                                                                                             |

| 5.1        | Introduction                                                                                                               |

|            | 5.1.1 Overview                                                                                                             |

|            | 5.1.2 Features                                                                                                             |

|            | 5.1.3 Modes of Operation                                                                                                   |

|            | 5.1.4 Block Diagram                                                                                                        |

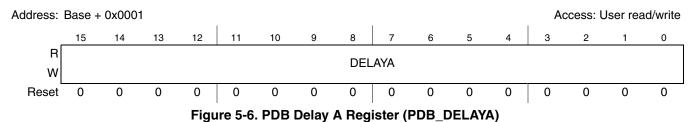

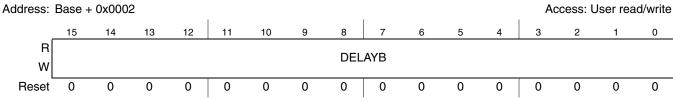

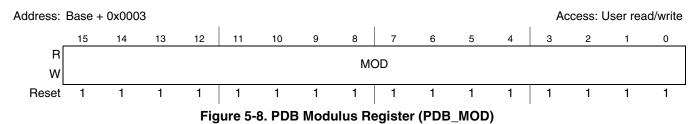

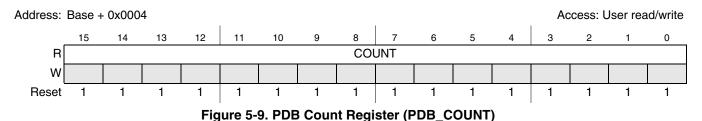

| 5.2        | Memory Map and Registers                                                                                                   |

|            | 5.2.1 Memory Map                                                                                                           |

|            | 5.2.2 Register Descriptions                                                                                                |

|            | 5.2.3 Functional Description                                                                                               |

| 5.3        | Resets                                                                                                                     |

| 5.4        | Interrupts                                                                                                                 |

|            |                                                                                                                            |

|            | Chapter 6                                                                                                                  |

|            | Dual Timer (DTMR)                                                                                                          |

| 6.1        | Introduction                                                                                                               |

|            | 6.1.1 Overview                                                                                                             |

|            | 6.1.2 Features                                                                                                             |

|            | 6.1.3 Mode of Operation                                                                                                    |

|            | 6.1.4 Block Diagram                                                                                                        |

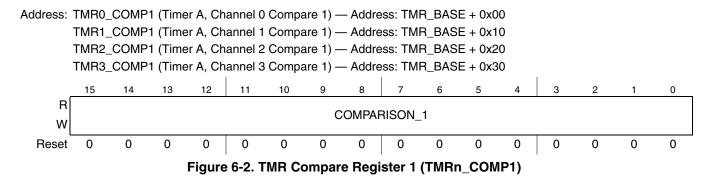

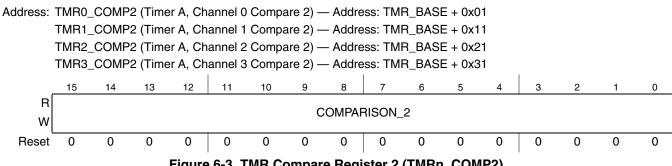

| 6.2        | Memory Map and Registers6-3                                                                                                |

|            | 6.2.1 Overview                                                                                                             |

|            | 6.2.2 Module Memory Map6-3                                                                                                 |

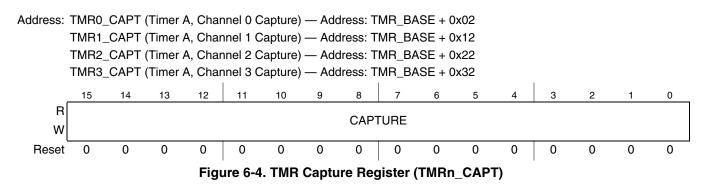

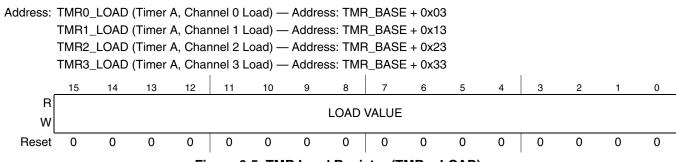

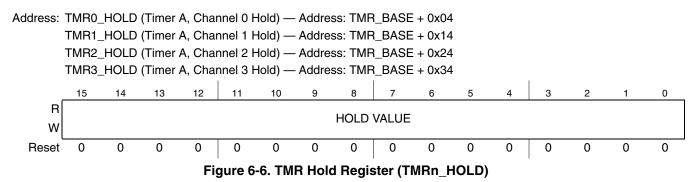

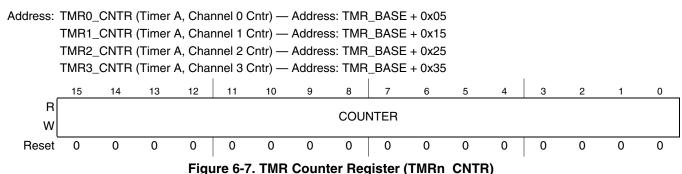

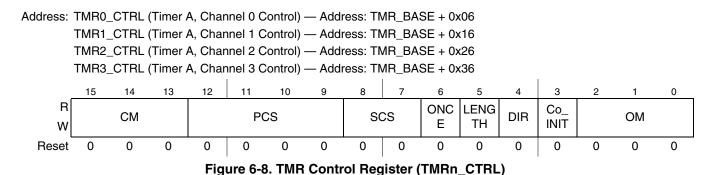

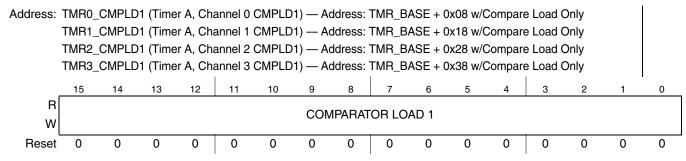

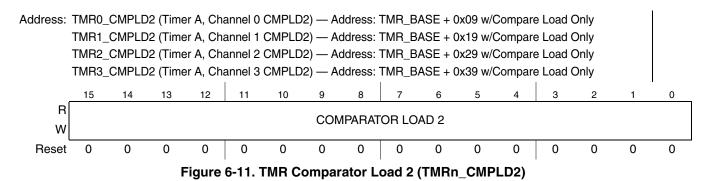

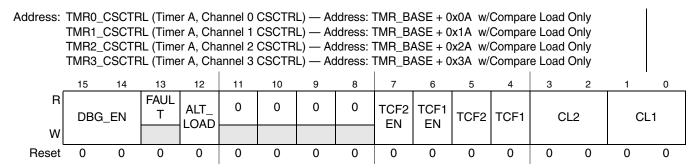

|            | 6.2.3 Register Descriptions                                                                                                |

| 6.3        | Functional Description                                                                                                     |

|            | 6.3.1 General                                                                                                              |

|            |                                                                                                                            |

|            | 6.3.2 Functional Modes                                                                                                     |

| 6.4        | 6.3.2 Functional Modes       6-17         Resets       6-32                                                                |

| 6.4        | 6.3.2 Functional Modes       6-17         Resets       6-32         6.4.1 General       6-32                               |

| 6.4<br>6.5 | 6.3.2 Functional Modes       6-17         Resets       6-32         6.4.1 General       6-32         Interrupts       6-32 |

|            | 6.3.2 Functional Modes       6-17         Resets       6-32         6.4.1 General       6-32                               |

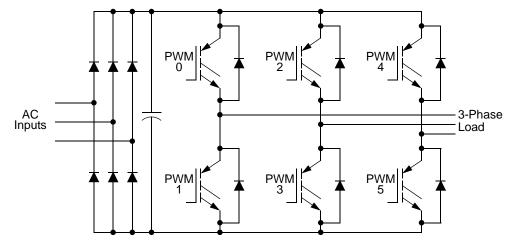

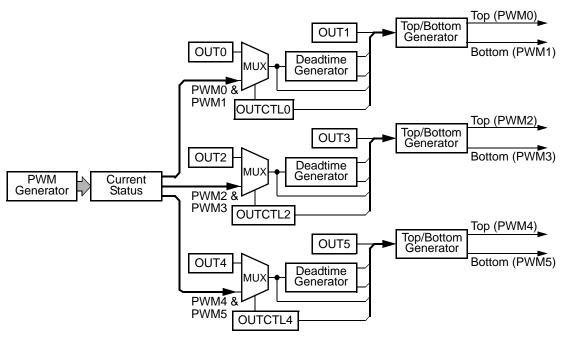

# Chapter 7 Pulse Width Modulator (PWM)

| 7.1 | Introduction                                                       | 7-1  |

|-----|--------------------------------------------------------------------|------|

|     | 7.1.1 Overview                                                     | 7-1  |

|     | 7.1.2 Features                                                     | 7-1  |

|     | 7.1.3 Modes of Operation                                           | 7-2  |

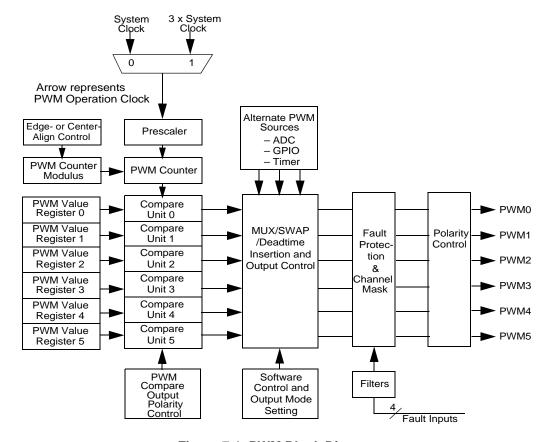

|     | 7.1.4 Block Diagrams                                               | 7-3  |

| 7.2 | Functional Description                                             | 7-3  |

|     | 7.2.1 Prescaler                                                    | 7-3  |

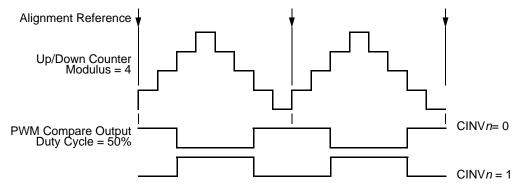

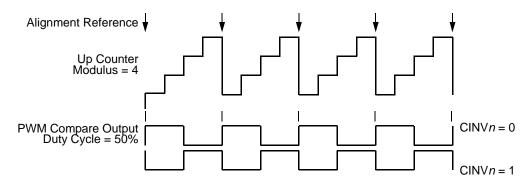

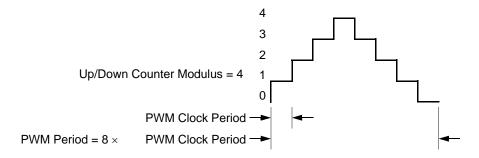

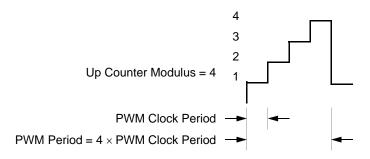

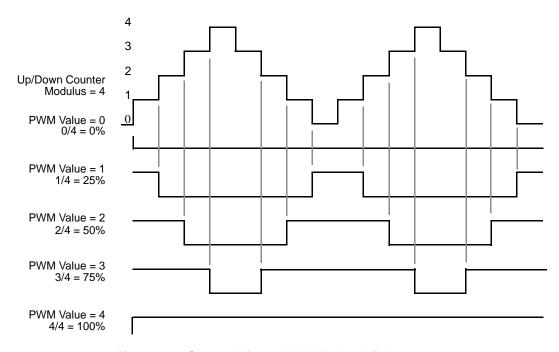

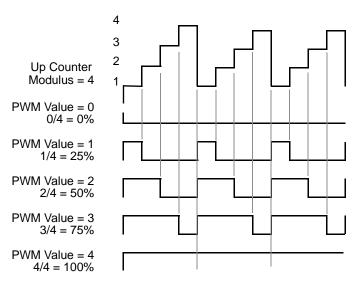

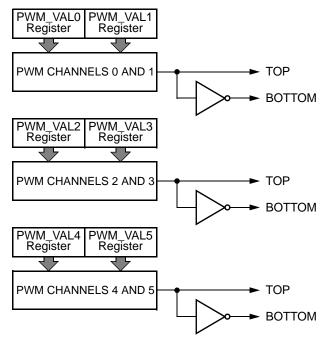

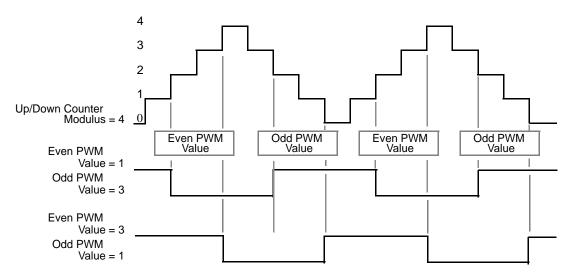

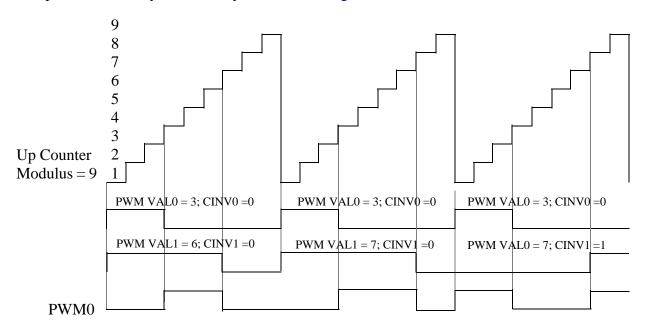

|     | 7.2.2 Generator                                                    | 7-3  |

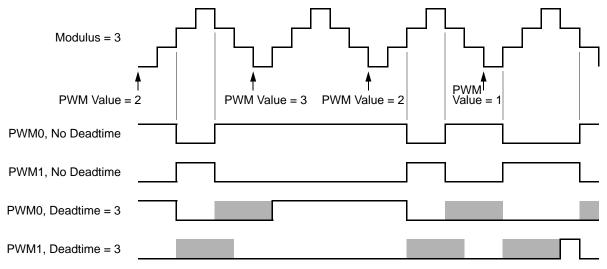

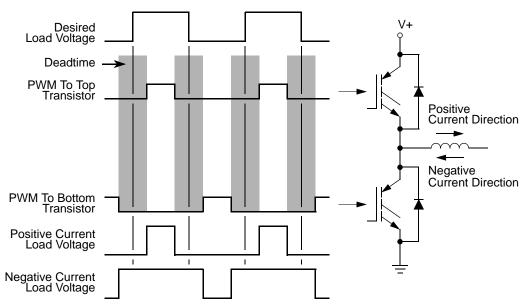

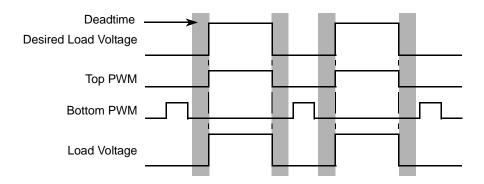

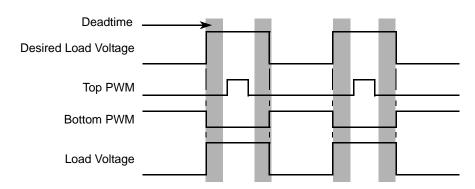

|     | 7.2.3 Independent or Complementary Channel Operation               | 7-7  |

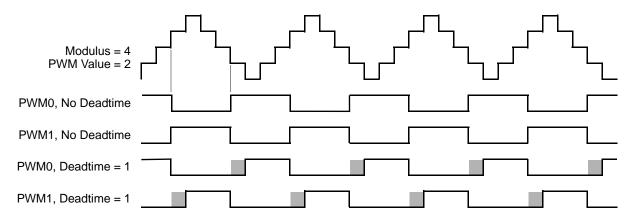

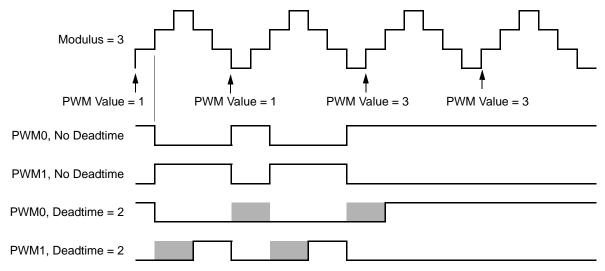

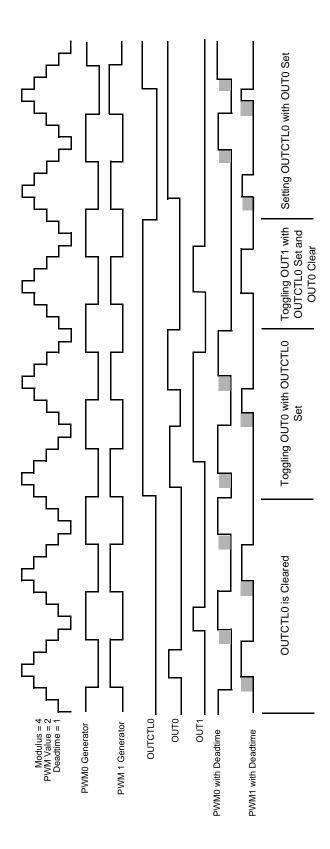

|     | 7.2.4 Deadtime Generators                                          | 7-8  |

|     | 7.2.5 Asymmetric PWM Output                                        | 7-13 |

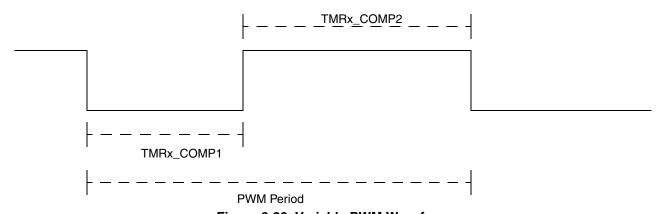

|     | 7.2.6 Variable Edge Placement PWM Output                           | 7-14 |

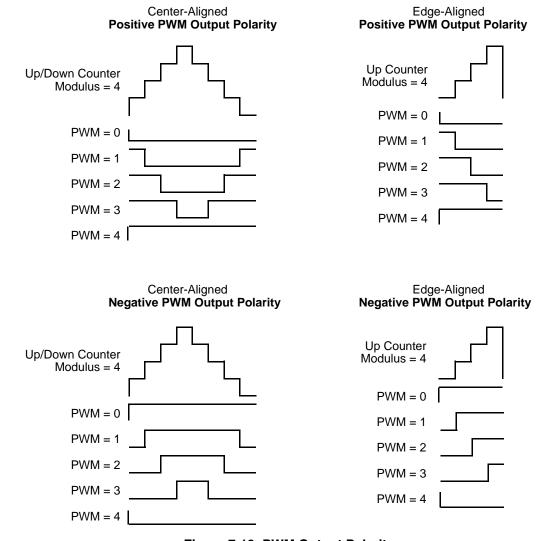

|     | 7.2.7 PWM Output Polarity                                          | 7-15 |

|     | 7.2.8 Software Output Control                                      | 7-16 |

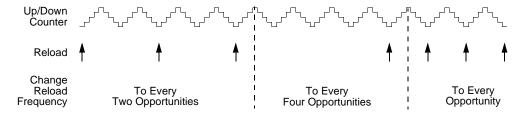

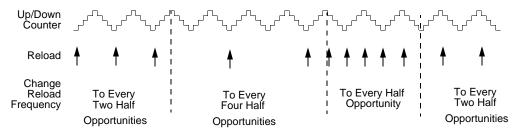

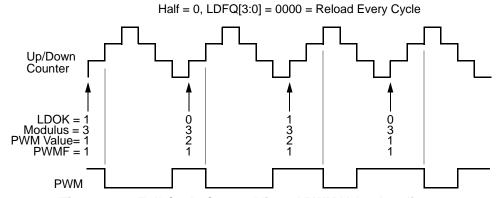

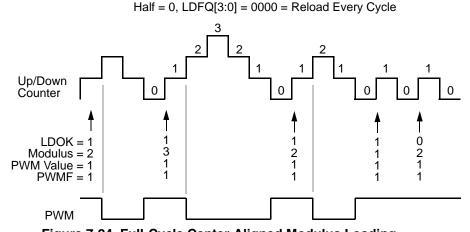

|     | 7.2.9 Generator Loading                                            | 7-18 |

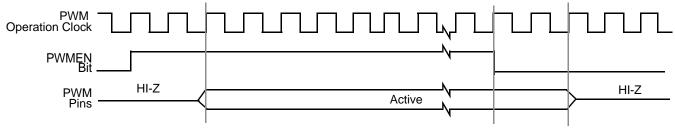

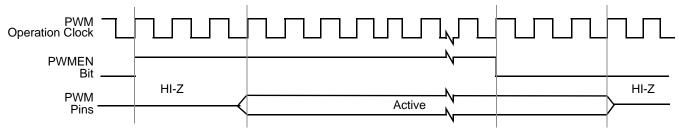

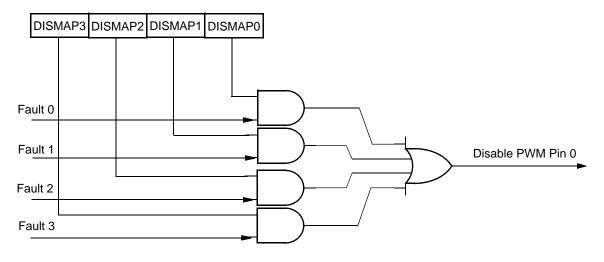

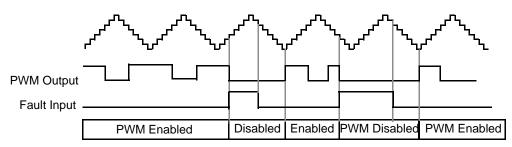

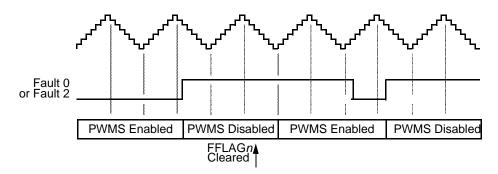

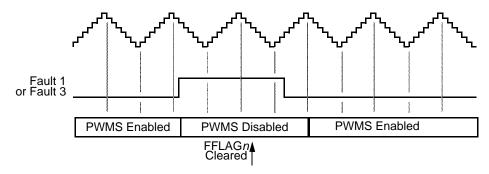

|     | 7.2.10 Fault Protection                                            |      |

|     | 7.2.11 External Synchronization of PWM Counting (EXT_SYNC)         | 7-25 |

| 7.3 | Signal Descriptions                                                |      |

|     | 7.3.1 PWM0–PWM5 Pins                                               | 7-25 |

|     | 7.3.2 FAULT0–FAULT3 Pins                                           |      |

|     | 7.3.3 Inter-module Connection Signals                              | 7-26 |

| 7.4 | Memory Map and Registers                                           | 7-26 |

|     | 7.4.1 Module Memory Map                                            | 7-26 |

|     | 7.4.2 Register Descriptions                                        |      |

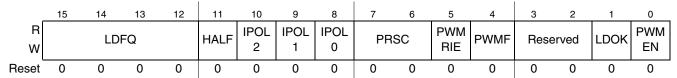

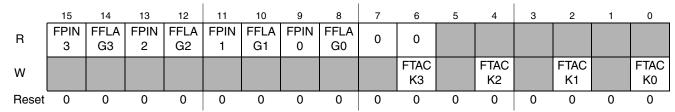

|     | 7.4.3 PWM Control Register (PWM_CTRL)                              |      |

|     | 7.4.4 PWM Fault Control Register (PWM_FCTRL)                       |      |

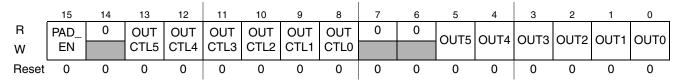

|     | 7.4.5 PWM Fault Status Acknowledge Register (PWM_FLTACK)           |      |

|     | 7.4.6 PWM Output Control Register (PWM_OUT)                        |      |

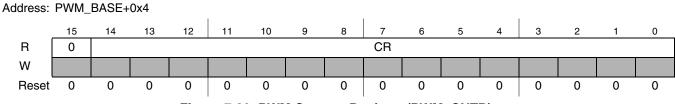

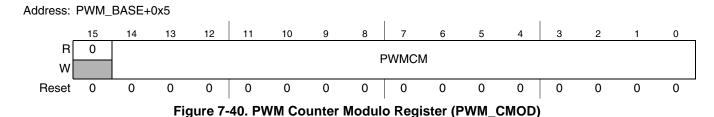

|     | 7.4.7 PWM Counter Modulo Register (PWM_CMOD)                       |      |

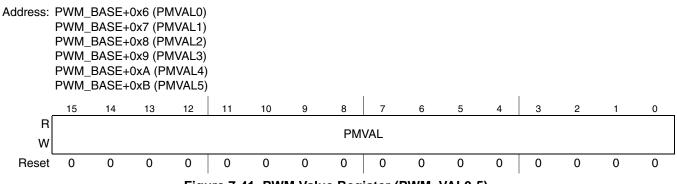

|     | 7.4.8 PWM Value Registers (PWM_VAL0-5)                             |      |

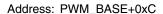

|     | 7.4.9 PWM Deadtime Registers (PWM_DTIM0, PWM_DTIM1)                |      |

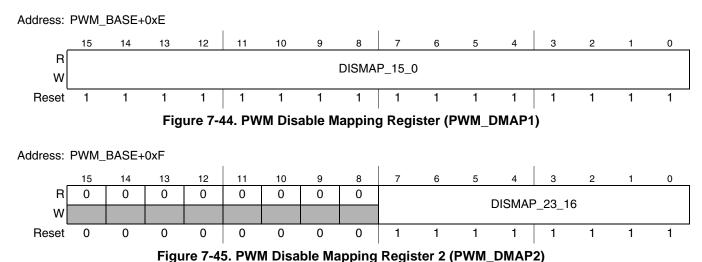

|     | 7.4.10 PWM Disable Mapping Registers (PWM_DMAP1-2)                 | 7-34 |

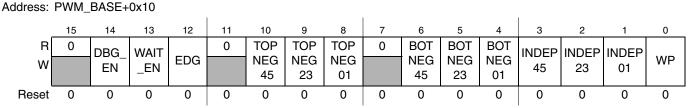

|     | 7.4.11 PWM Configure Register (PWM_CNFG)                           |      |

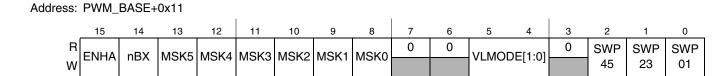

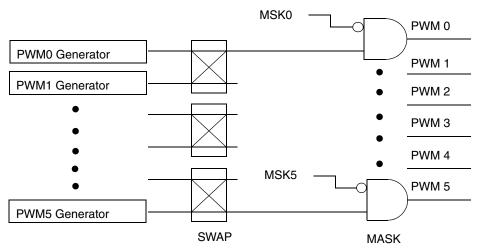

|     | 7.4.12 PWM Channel Control Register (PWM_CCTRL)                    |      |

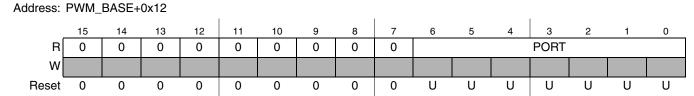

|     | 7.4.13 PWM Port Register (PWM_PORT)                                | 7-38 |

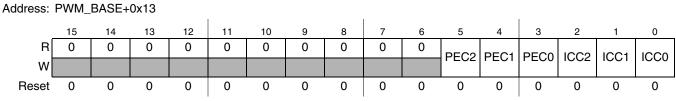

|     | 7.4.14 PWM Internal Correction Control Register (PWM_ICCTRL)       |      |

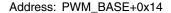

|     | 7.4.15 PWM Source Control Register (PWM_SCTRL)                     |      |

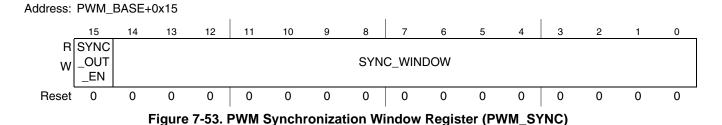

|     | 7.4.16 PWM Synchronization Window Register (PWM_SYNC)              | 7-41 |

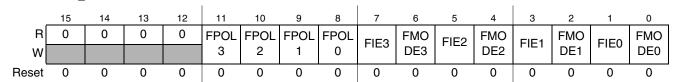

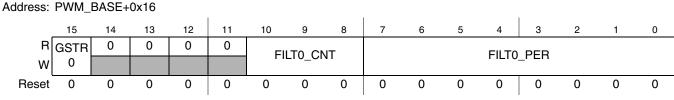

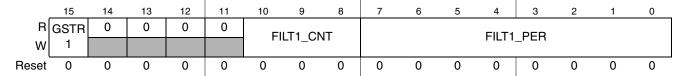

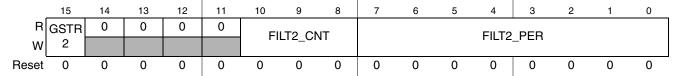

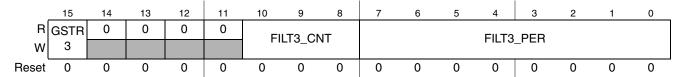

|     | 7.4.17 Fault Filter Registers (PWM_FFILT0, PWM_FFILT1, PWM_FFILT2, |      |

|     | PWM_FFILT3)                                                        |      |

| 7.5 | Resets                                                             |      |

| 7.6 | Clocks                                                             |      |

| 7.7 | Interrupts                                                         | 7-43 |

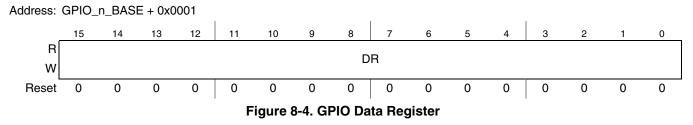

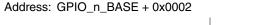

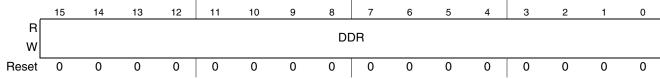

## Chapter 8 General-Purpose Input/Output (GPIO)

| 8.1 | Overview                                             |        |

|-----|------------------------------------------------------|--------|

|     | 8.1.1 Features                                       |        |

|     | 8.1.2 Modes of Operation                             |        |

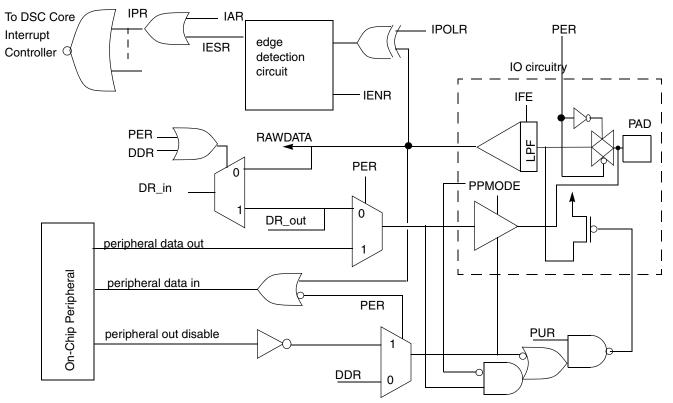

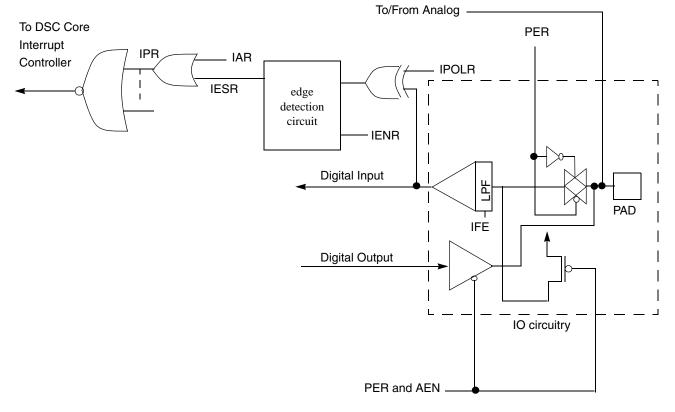

|     | 8.1.3 Block Diagram                                  |        |

| 8.2 | GPIO Interrupts                                      |        |

| 8.3 | Clocks and Resets                                    |        |

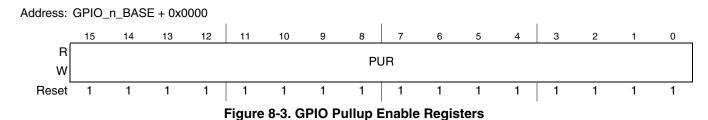

| 8.4 | Memory Map and Registers                             |        |

|     | 8.4.1 Module Memory Map                              |        |

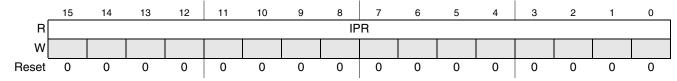

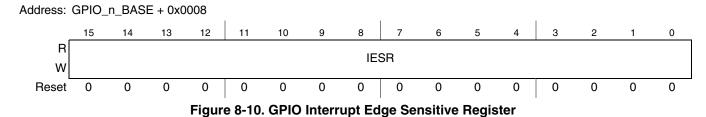

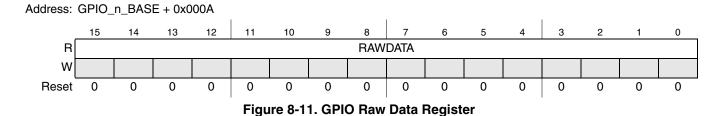

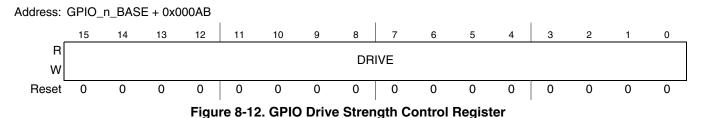

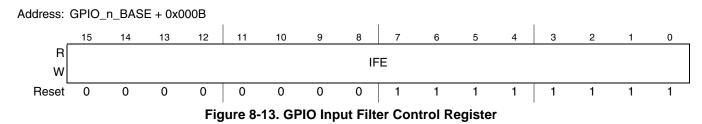

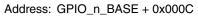

|     | 8.4.2 Register Descriptions                          | 8-5    |

|     | Chapter 9                                            |        |

|     | Inter-Integrated Circuit (I <sup>2</sup> C)          |        |

| 9.1 | Introduction                                         | 9-1    |

|     | 9.1.1 Features                                       |        |

|     | 9.1.2 Modes of Operation                             | 9-1    |

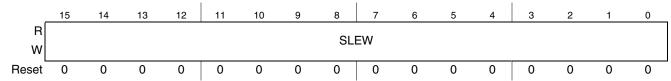

|     | 9.1.3 Block Diagram                                  |        |

| 9.2 | External Signal Description                          |        |

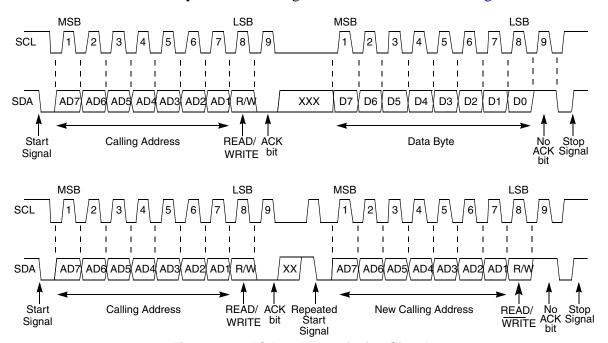

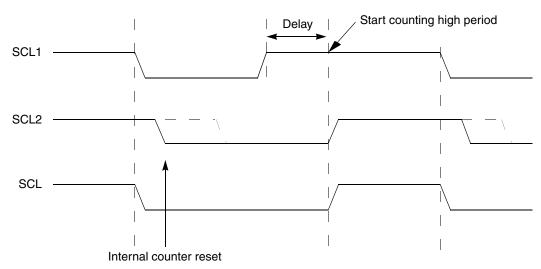

|     | 9.2.1 SCL — Serial Clock Line                        | 9-2    |

|     | 9.2.2 SDA — Serial Data Line                         | 9-2    |

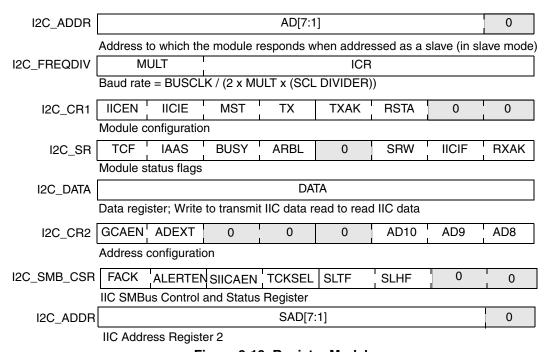

| 9.3 | Register Definition                                  | 9-3    |

|     | 9.3.1 Module Memory Map                              | 9-3    |

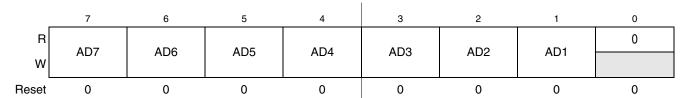

|     | 9.3.2 IIC Address Register 1 (IICA1)                 | 9-4    |

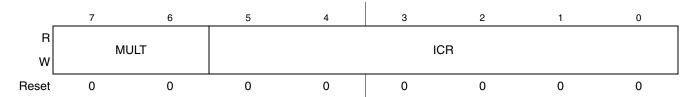

|     | 9.3.3 IIC Frequency Divider Register (IICF)          | 9-4    |

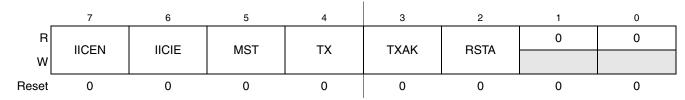

|     | 9.3.4 IIC Control Register (IICC1)                   | 9-6    |

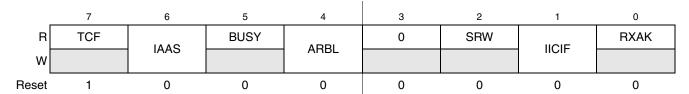

|     | 9.3.5 IIC Status Register (IICS)                     | 9-7    |

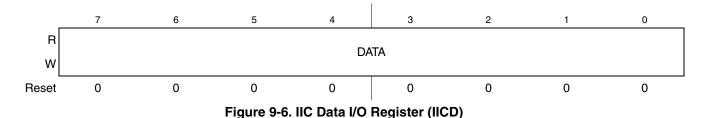

|     | 9.3.6 IIC Data I/O Register (IICD)                   |        |

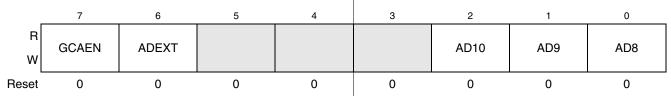

|     | 9.3.7 IIC Control Register 2 (IICC2)                 |        |

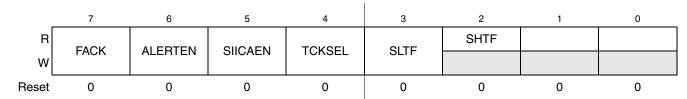

|     | 9.3.8 IIC SMBus Control and Status Register (IICSMB) | . 9-10 |

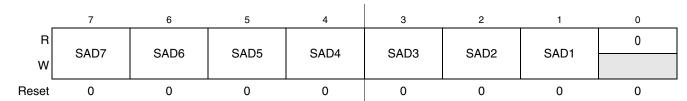

|     | 9.3.9 IIC Address Register 2 (I2C_ADDR)              | . 9-11 |

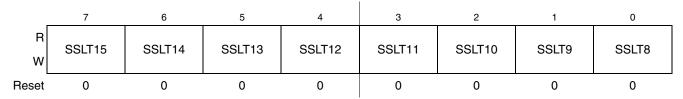

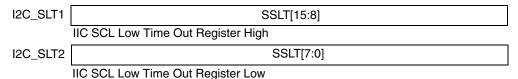

|     | 9.3.10 IIC SCL Low Time Out Register High (I2C_SLT1) | . 9-12 |

|     | 9.3.11 IIC SCL Low Time Out register Low (I2C_SLT2)  |        |

| 9.4 | Functional Description                               | _      |

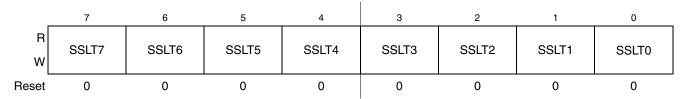

|     | 9.4.1 IIC Protocol                                   |        |

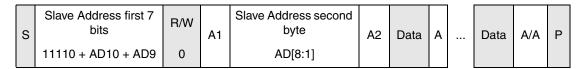

|     | 9.4.2 10-bit Address                                 |        |

|     | 9.4.3 Address Matching                               |        |

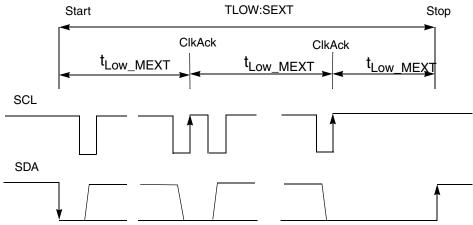

|     | 9.4.4 System Management Bus Specification            |        |

| 9.5 | Resets                                               |        |

| 9.6 | Interrupts                                           |        |

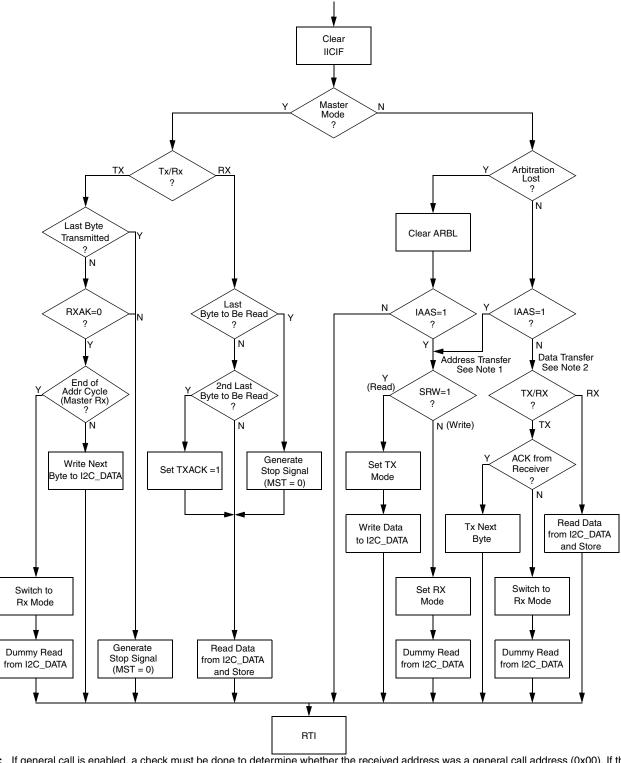

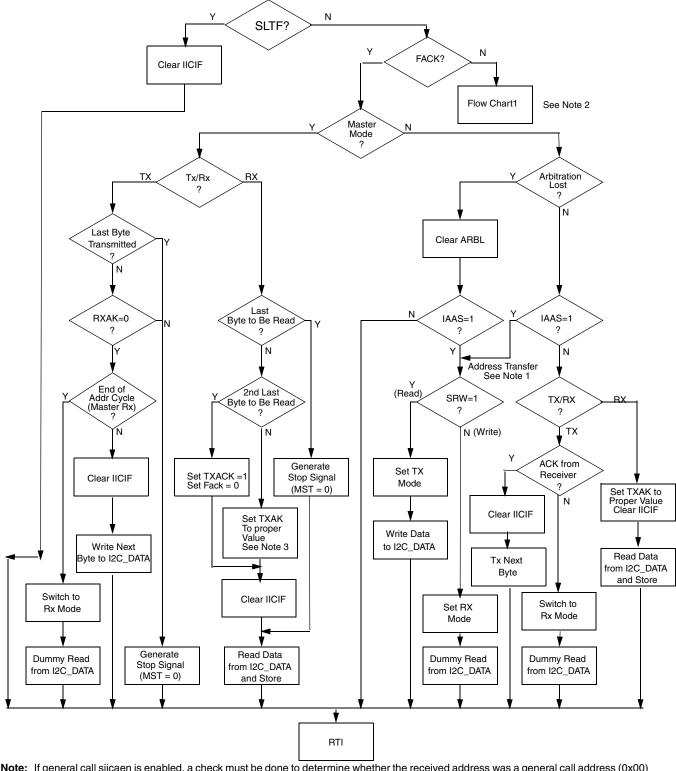

|     | 9.6.1 Byte Transfer Interrupt                        |        |

|     | 9.6.2 Address Detect Interrupt                       |        |

|     | 9.6.3 Arbitration Lost Interrupt                     |        |

|     | 9.6.4 Timeouts Interrupt in SMbus                    | . 9-21 |

| 9.7  | Initialization/Application Information    | 9-21  |

|------|-------------------------------------------|-------|

|      | 9.7.1 Module Initialization (Slave)       | 9-21  |

|      | 9.7.2 Module Initialization (Master)      | 9-21  |

|      | 9.7.3 Module Use                          |       |

|      |                                           |       |

|      | Chapter 10                                |       |

|      | Serial Communications Interface (SCI)     |       |

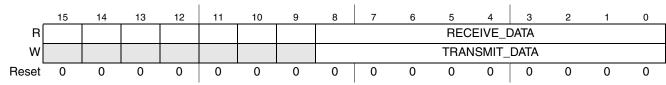

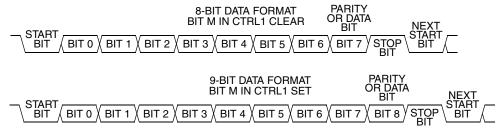

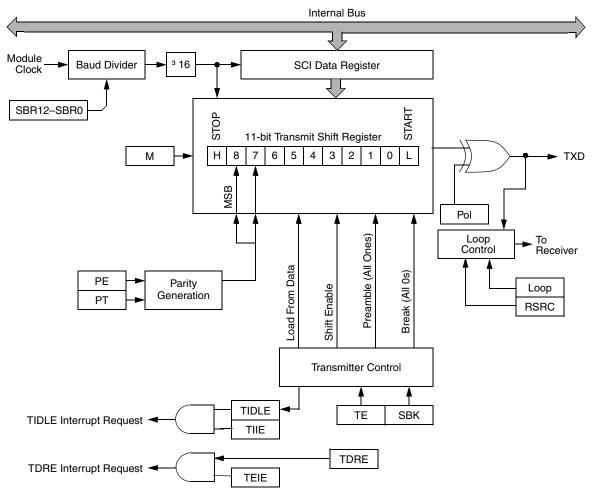

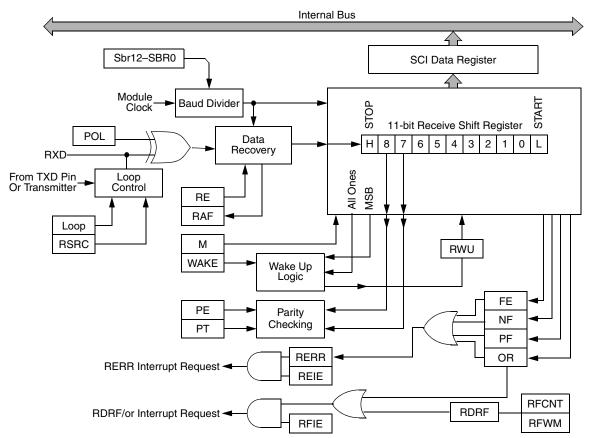

| 10.1 | Overview                                  | 10-1  |

|      | Features                                  |       |

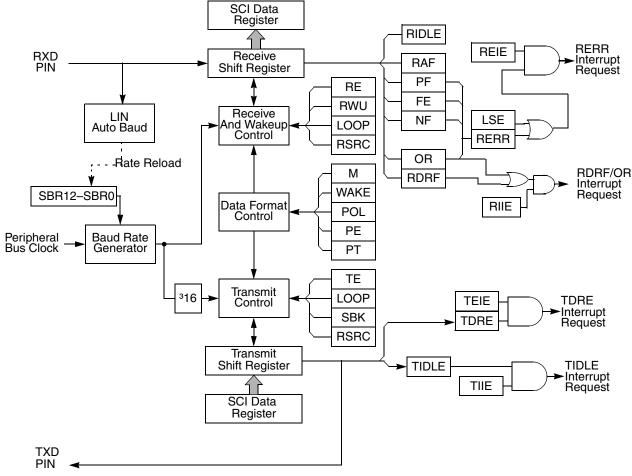

|      | Block Diagram                             |       |

|      | Signal Descriptions                       |       |

| 10.4 | 10.4.1 Overview                           |       |

|      | 10.4.2 External Pin Descriptions          |       |

| 10.5 | Memory Map and Registers                  |       |

| 10.5 | 10.5.1 Overview                           |       |

|      | 10.5.2 Module Memory Map                  |       |

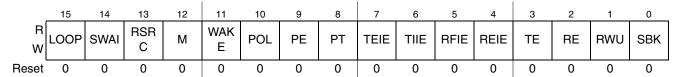

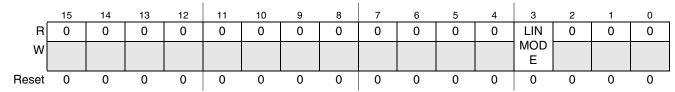

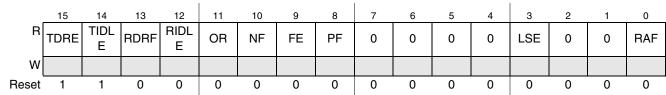

|      | 10.5.3 Register Descriptions              |       |

| 10.6 | Functional Description                    |       |

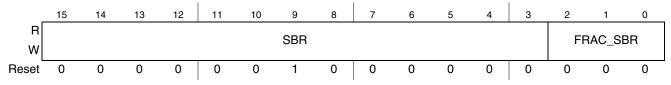

| 10.0 | 10.6.1 General                            |       |

| 10.7 | Resets                                    |       |

|      | Clocks                                    |       |

|      | Interrupts                                |       |

| 10.5 | 10.9.1 General                            |       |

|      | 10.9.2 Description of Interrupt Operation |       |

|      | 10.0.2 Decomption of interrupt operation  | 10 20 |

|      | Chapter 11                                |       |

|      | Serial Peripheral Interface (SPI)         |       |

| 44.4 | •                                         | 44.4  |

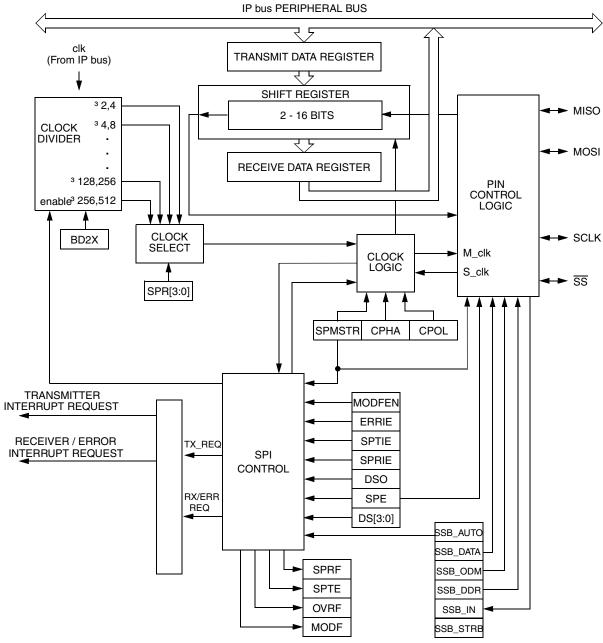

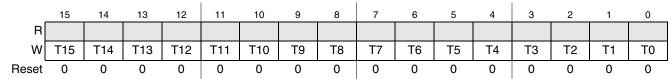

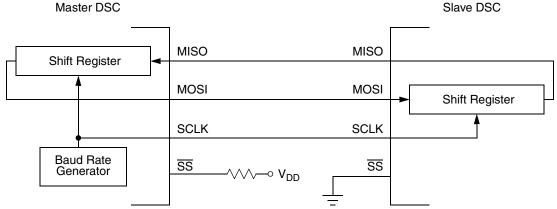

| 11.1 | Introduction                              |       |

|      | 11.1.1 Overview                           |       |

| 11.0 | 11.1.2 Block Diagram                      |       |

|      | Signal Descriptions                       |       |

|      | 11.2.1 External I/O Signals               |       |

| 11.0 | 11.2.2 MISO (Master In/Slave Out)         |       |

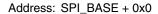

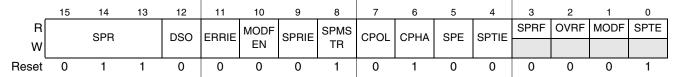

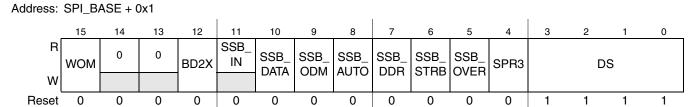

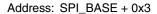

| 11.3 | Memory Map and Registers                  |       |

|      | 11.3.1 Module Memory Map                  |       |

| 44 / | 11.3.2 Register Descriptions              |       |

| 11.4 | Functional Description                    |       |

|      | 11.4.1 Operating Modes                    |       |

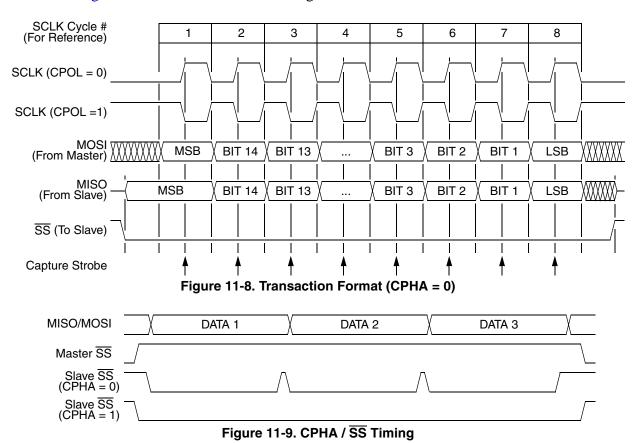

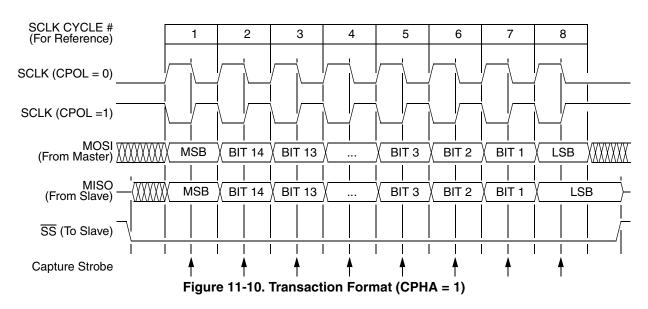

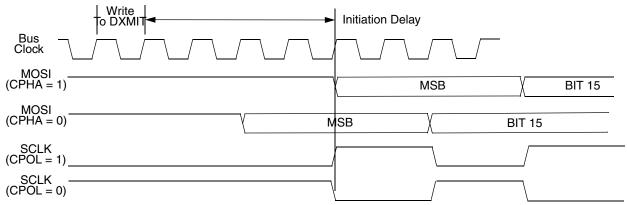

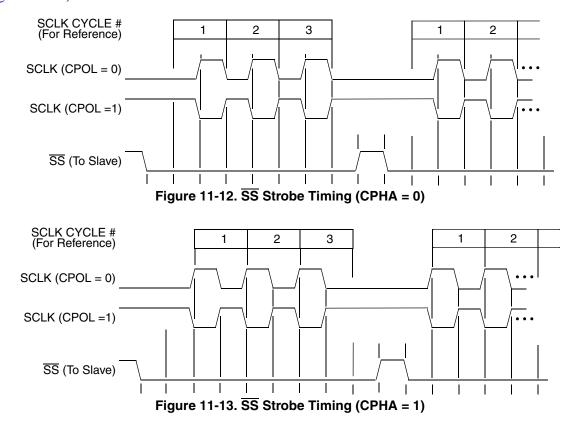

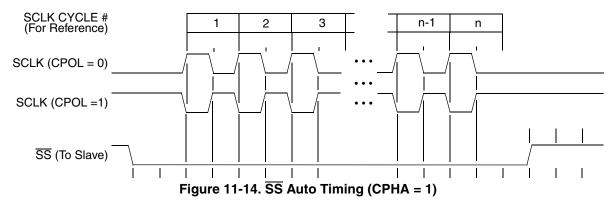

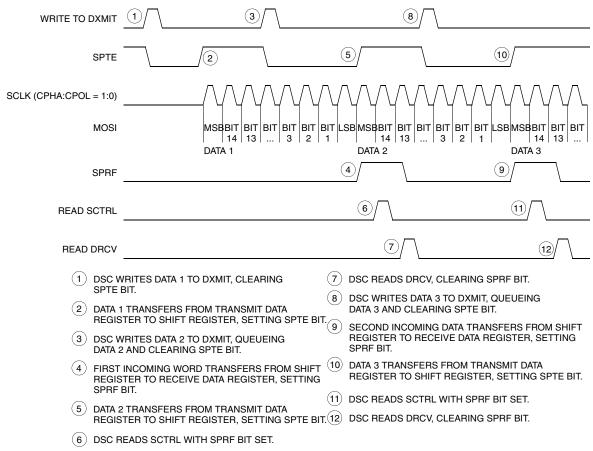

|      | 11.4.2 Transaction Formats                |       |

|      | 11.4.3 Transmission Data                  |       |

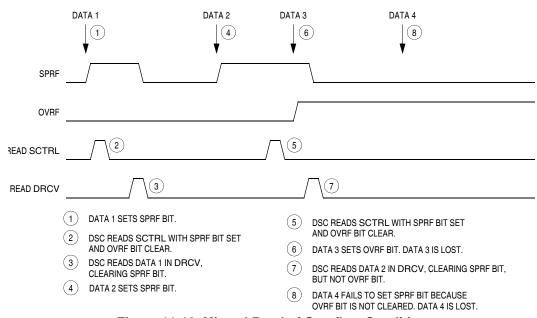

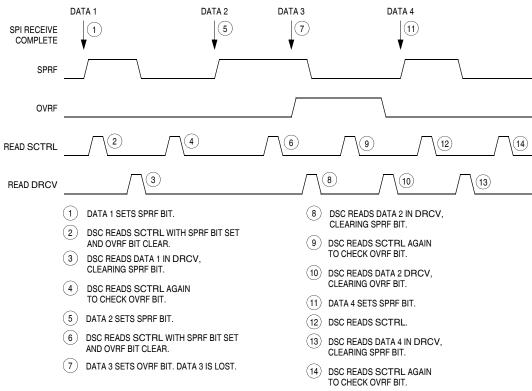

|      | 11.4.4 Error Conditions                   |       |

| 44.5 | 11.4.5 Resetting the SPI                  |       |

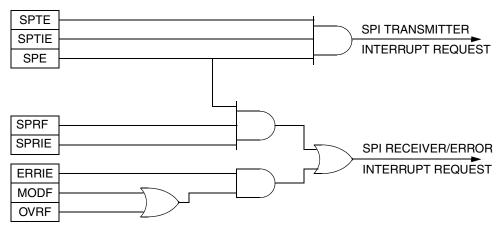

| 11.5 | Interrupts                                | 11-23 |

# Chapter 12 Interrupt Controller (WINTC)

| 12.1 | Introduction                                                | 12-1    |

|------|-------------------------------------------------------------|---------|

|      | 12.1.1 Overview                                             | 12-1    |

|      | 12.1.2 Features                                             | 12-1    |

|      | 12.1.3 Modes of Operation                                   | 12-2    |

|      | 12.1.4 Block Diagram                                        |         |

| 12.2 | Functional Description                                      |         |

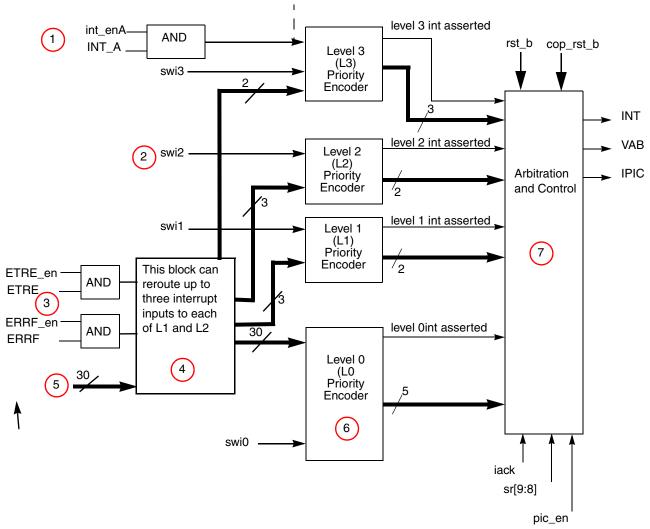

|      | 12.2.1 Discussion of the Interrupt Controller Block Diagram | 12-3    |

|      | 12.2.2 Overview                                             |         |

|      | 12.2.3 Normal Interrupt Handling                            | 12-5    |

|      | 12.2.4 Interrupt Nesting                                    |         |

|      | 12.2.5 Fast Interrupt Handling                              |         |

| 12.3 | Memory Map and Registers                                    |         |

|      | 12.3.1 Interrupt Vector Table                               | 12-6    |

|      | 12.3.2 Module Memory Map                                    |         |

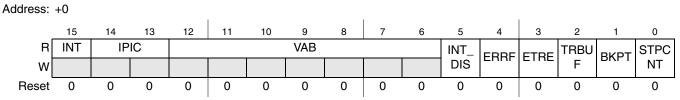

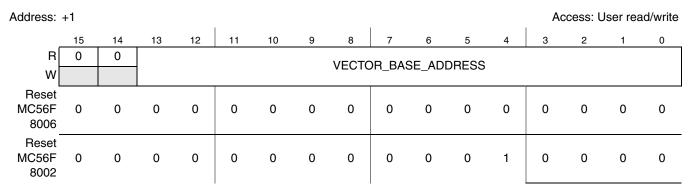

|      | 12.3.3 Register Descriptions                                |         |

| 12.4 | Resets                                                      | . 12-13 |

|      |                                                             |         |

|      | Chapter 13                                                  |         |

|      | On-Chip Clock Synthesis (OCCS)                              |         |

| 13.1 | Introduction                                                |         |

|      | 13.1.1 Overview                                             |         |

|      | 13.1.2 Features                                             |         |

| 13.2 | Modes of Operation                                          |         |

|      | 13.2.1 Internal Clock Source                                |         |

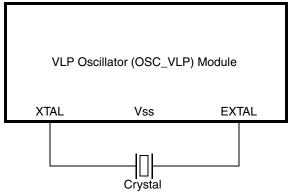

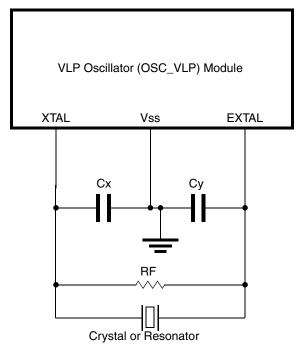

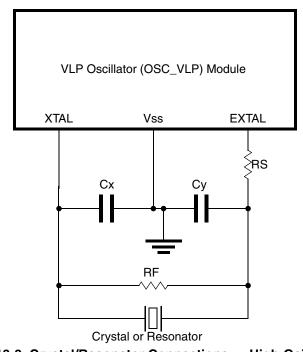

|      | 13.2.2 Crystal (or Ceramic Resonator) Oscillator            |         |

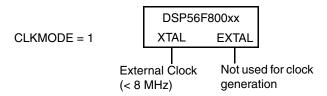

|      | 13.2.3 External Clock Source — Crystal Oscillator Option    |         |

|      | 13.2.4 External Clock Source — GPIO                         |         |

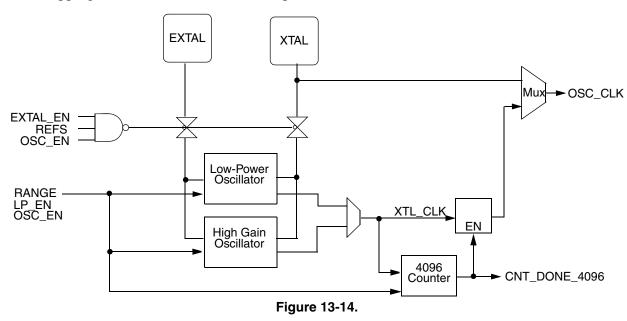

|      | Block Diagram                                               |         |

| 13.4 | Pin Descriptions                                            |         |

|      | 13.4.1 External Reference                                   |         |

|      | 13.4.2 Oscillator Inputs (XTAL, EXTAL)                      |         |

| 40.5 | 13.4.3 CLKO                                                 | 13-/    |

| 13.5 | Memory Map and Registers                                    |         |

| 40.0 | 13.5.1 Module Memory Map                                    |         |

| 13.6 | Register Descriptions                                       | 13-8    |

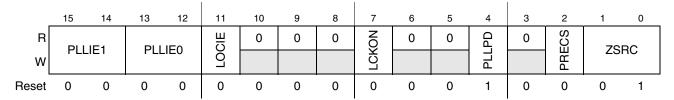

|      | 13.6.1 PLL Control Register (OCCS_CTRL)                     |         |

|      | 13.6.2 PLL Divide-By Register (OCCS_DIVBY)                  |         |

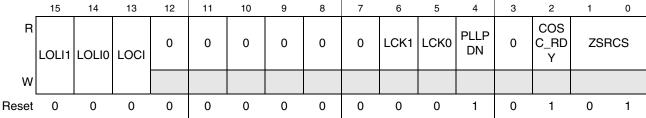

|      | 13.6.3 OCCS Status Register (OCCS_STAT)                     |         |

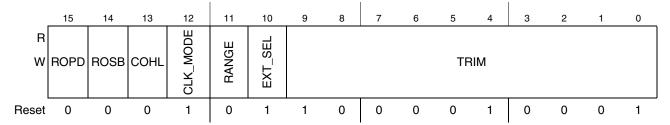

|      | 13.6.4 Oscillator Control Register (OCCS_OSCTL)             |         |

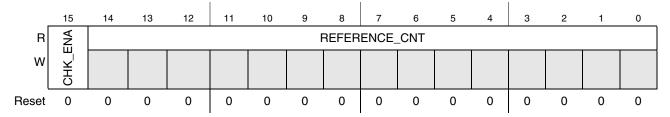

|      | 13.6.5 External Clock Check (OCCS_CLKCHKR and OCCS_CLKCHKT) |         |

| 107  | 13.6.6 Protection Register (OCCS_PROT)                      |         |

| 13.7 | Functional Description                                      | . 13-15 |

| 13.8 Helaxation Oscillator                                                   |       |

|------------------------------------------------------------------------------|-------|

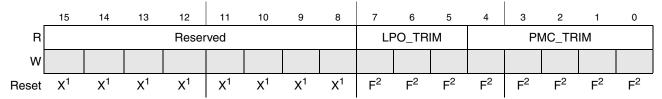

| 13.8.1 Trimming Frequency on the Internal Relaxation Oscillator              | 13-19 |

| 13.9 External Reference                                                      | 13-19 |

| 13.10Crystal Oscillator                                                      |       |

| 13.10.1Switching Clock Sources                                               | 13-19 |

| 13.11Phase Locked Loop                                                       |       |

| 13.11.1PLL Recommended Range of Operation                                    |       |

| 13.11.2PLL Lock Time Specification                                           |       |

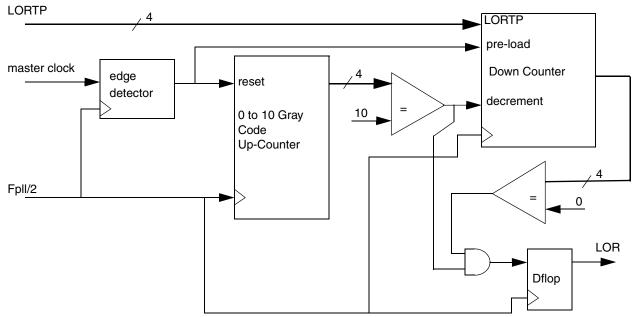

| 13.12PLL Frequency Lock Detector Block                                       |       |

| 13.13Loss of Reference Clock Detector                                        |       |

| 13.14Clocks                                                                  |       |

| 13.15Interrupts                                                              |       |

|                                                                              |       |

| Chapter 14                                                                   |       |

| System Integration Module (SIM)                                              |       |

| 14.1 Introduction                                                            | 1.4_1 |

| 14.1.1 Overview                                                              |       |

| 14.1.2 References                                                            |       |

| 14.1.3 Features                                                              |       |

| 14.1.4 Modes of Operation                                                    |       |

| 14.1.5 Run Mode                                                              |       |

| 14.1.6 Debug Mode                                                            |       |

| 14.1.7 Wait Mode                                                             |       |

| 14.1.8 Stop Mode                                                             |       |

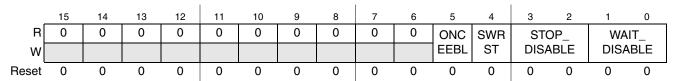

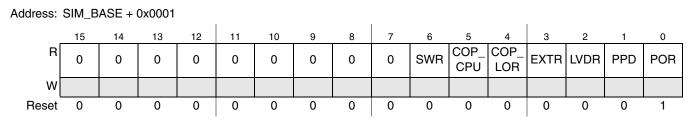

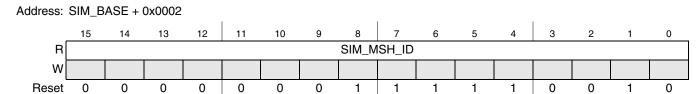

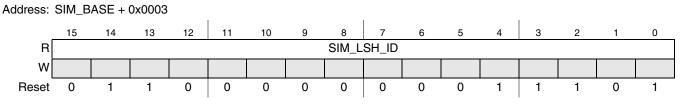

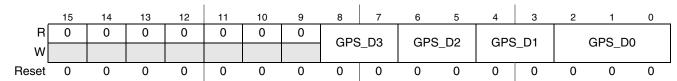

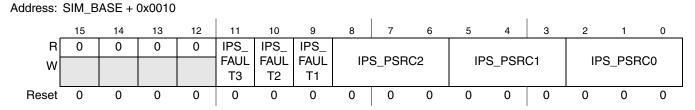

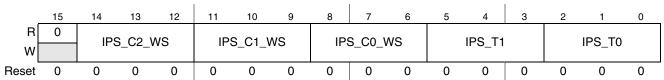

| 14.2 Memory Map and Registers                                                |       |

| 14.2.1 Module Memory Map                                                     |       |

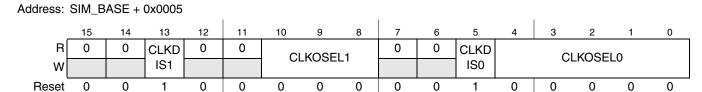

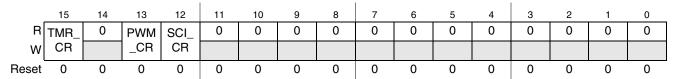

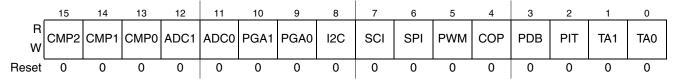

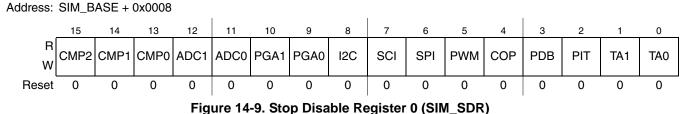

| 14.2.2 Register Descriptions                                                 |       |

| 14.3 Functional Descriptions                                                 |       |

| 14.3.1 Clock Generation Overview                                             |       |

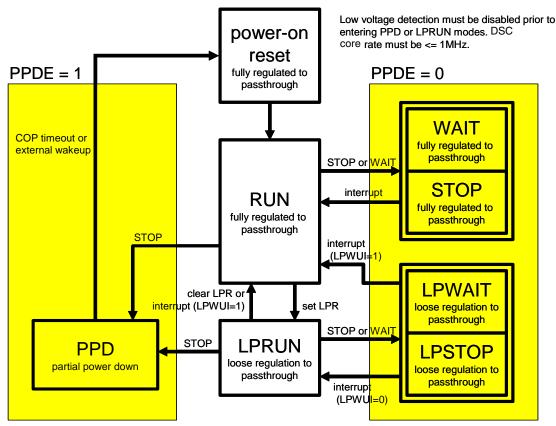

| 14.3.2 Power-Down Modes Overview                                             | _     |

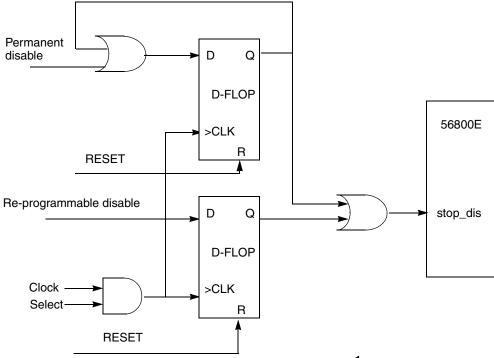

| 14.3.3 Stop and Wait Mode Disable Function                                   |       |

| 14.4 Resets                                                                  |       |

| 14.5 Clocks                                                                  |       |

| 14.6 Interrupts                                                              |       |

|                                                                              |       |

| Chapter 15                                                                   |       |

| Power Management Controller (PMC)                                            |       |

| 15.1 Overview                                                                | 15-1  |

| 15.2 Features                                                                |       |

| 15.3 Power Management Methodologies                                          |       |

| 15.4 Initiating and Recovering from Partial Power-Down Mode                  |       |

| 15.5 Power Management Controller Functional Operation                        |       |

| 15.5.1 Power-On Reset Operation                                              |       |

| 15.5.2 Low-Voltage Detect (LVD) System                                       |       |

| . S.S.E EST TOTAGE BOTOST (ETB) Cyclotti 11111111111111111111111111111111111 |       |

Х

|       | 15.5.3 Out-of-Regulation (OOR) Interrupt Operation | 15-5        |

|-------|----------------------------------------------------|-------------|

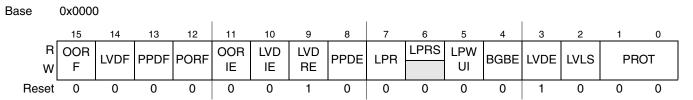

| 15.6  | PMC Programmer's Model                             | 15-5        |

|       | 15.6.1 PMC Status and Control Register (PMC_SCR)   | 15-6        |

|       | 15.6.2 PMC Control Register 2 (PMC_CR2)            | 15-7        |

|       | Ohambar 4C                                         |             |

|       | Chapter 16 Computer Operating Properly (COP)       |             |

| 101   | Computer Operating Properly (COP)                  | 404         |

| 16.1  | Introduction                                       |             |

|       | 16.1.2 References                                  |             |

| 16.2  | Features                                           |             |

|       | Partial Powerdown Operation                        |             |

|       | Block Diagram                                      |             |

|       | Signal Description                                 |             |

| 10.5  | 16.5.1 Overview                                    |             |

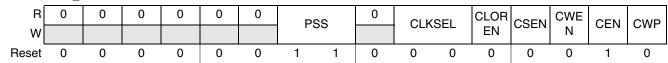

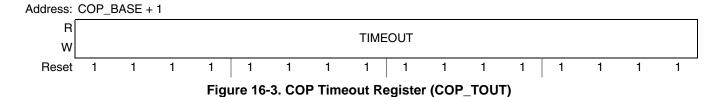

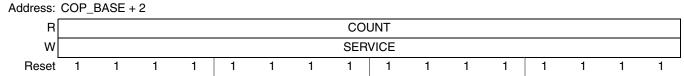

| 16.6  | Memory Map and Registers                           |             |

| 10.0  | 16.6.1 Register Descriptions                       |             |

| 16.7  | Functional Description                             |             |

|       | 16.7.1 General                                     |             |

|       | 16.7.2 Timeout Specifications                      |             |

|       | 16.7.3 COP after Reset                             |             |

|       | 16.7.4 Wait Mode Operation                         | 16-6        |

|       | 16.7.5 Stop Mode Operation                         | <b>16-6</b> |

|       | 16.7.6 Partial Power Down Mode Operation           | 16-6        |

|       | 16.7.7 Debug Mode Operation                        | 16-7        |

|       | 16.7.8 Loss of Reference Operation                 | 16-7        |

|       | <b>A</b> 1                                         |             |

|       | Chapter 17                                         |             |

|       | Real-Time Counter (RTC)                            |             |

| 17.1  | Introduction                                       |             |

|       | 17.1.1 Features                                    |             |

|       | 17.1.2 Modes of Operation                          |             |

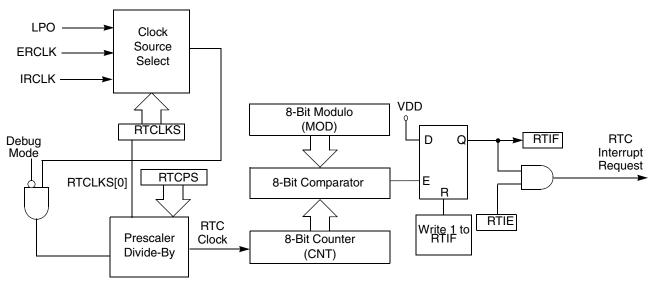

|       | 17.1.3 Block Diagram                               |             |

|       | External Signal Description                        |             |

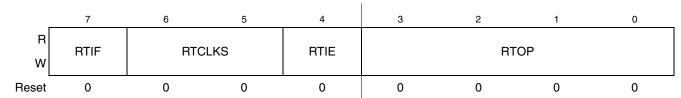

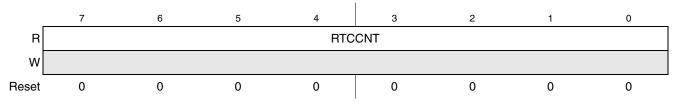

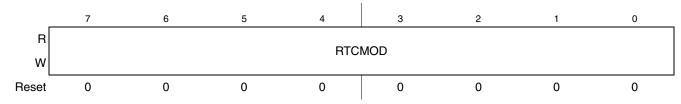

| 17.3  | Register Definitions                               | 17-2        |

|       | 17.3.1 RTC Status and Control Register (RTC_SC)    |             |

|       | 17.3.2 RTC Counter Register (RTC_CNT)              |             |

| 4 - 4 | 17.3.3 RTC Modulo Register (RTC_MOD)               |             |

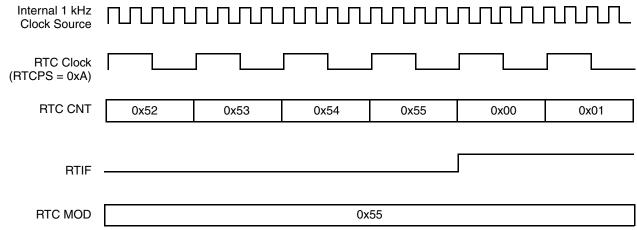

| 17.4  | Functional Description                             | 17-4        |

| 47 -  | 17.4.1 RTC Operation Example                       |             |

| 17.5  | Initialization/Application Information             | 17-6        |

Freescale Semiconductor xi

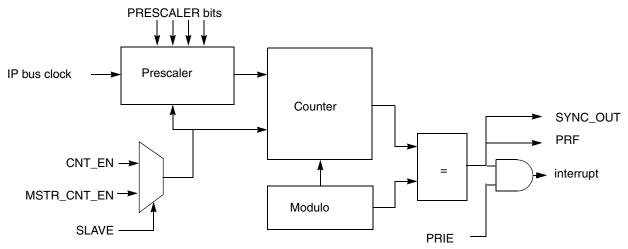

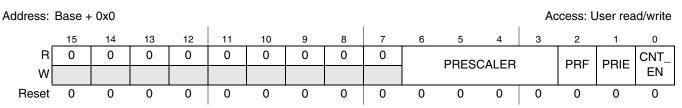

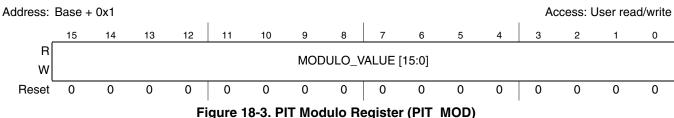

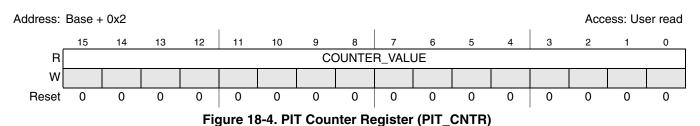

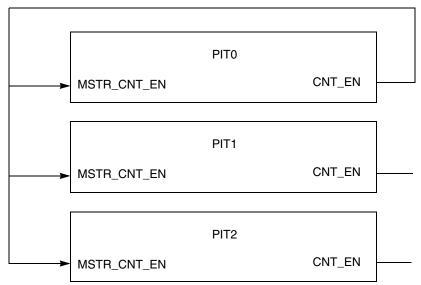

## Chapter 18 Programmable Interval Timer (PIT)

| 18.1 | Introduction                              | 18-1 |

|------|-------------------------------------------|------|

|      | 18.1.1 Overview                           | 18-1 |

|      | 18.1.2 Features                           |      |

|      | 18.1.3 Modes of Operation                 |      |

|      | 18.1.4 Block Diagram                      |      |

| 18.2 | Memory Map and Registers                  |      |

|      | 18.2.1 Overview                           |      |

|      | 18.2.2 Module Memory Map                  | 18-2 |

|      | 18.2.3 Register Descriptions              |      |

| 18.3 | Functional Description                    |      |

|      | 18.3.1 General                            |      |

|      | 18.3.2 Slave Mode                         |      |

|      | 18.3.3 Low Power Modes                    |      |

| 18.4 | Interrupts                                |      |

|      | 18.4.1 General                            |      |

|      |                                           |      |

|      | Chapter 19                                |      |

|      | Flash Memory (HFM)                        |      |

| 10.1 | Introduction                              | 10.1 |

| 19.1 |                                           |      |

|      | 19.1.1 Overview                           |      |

|      | 19.1.2 Features                           |      |

| 100  | 19.1.3 Block Diagram                      |      |

| 19.2 | Memory Map and Registers                  |      |

|      | 19.2.1 Overview                           |      |

|      | 19.2.2 Module Memory Map                  |      |

| 400  | 19.2.3 Register Descriptions              |      |

| 19.3 | Functional Description                    |      |

|      | 19.3.1 General                            |      |

|      | 19.3.2 Flash Use                          |      |

| 40.4 | 19.3.3 Flash Security Operation           |      |

| 19.4 | Resets                                    |      |

| 40 5 | 19.4.1 General                            |      |

| 19.5 | Interrupts                                |      |

|      | 19.5.1 General                            |      |

|      | 19.5.2 Description of Interrupt Operation | 9-25 |

|      | Chapter 20                                |      |

|      | Chapter 20                                |      |

|      | Joint Test Action Group Port (JTAG)       |      |

|      | Introduction                              |      |

| 20.2 | Features                                  | 20-1 |

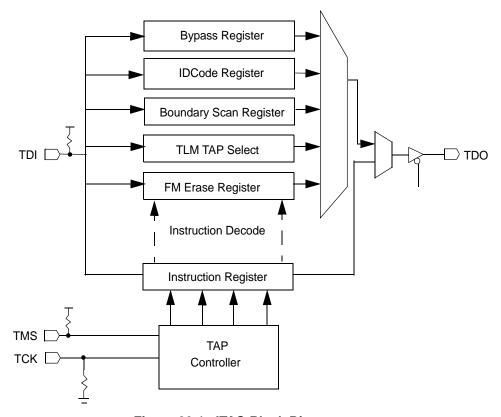

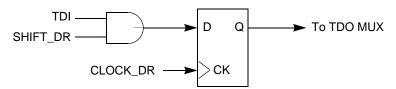

| 20.3 | Block Diagram                             | 20-2 |

|      | Functional Description                    |      |

|      |                                           |      |

|      | 20.4.1 JTAG Port Architecture  | 20-2 |

|------|--------------------------------|------|

|      | 20.4.2 Master TAP Instructions | 20-3 |

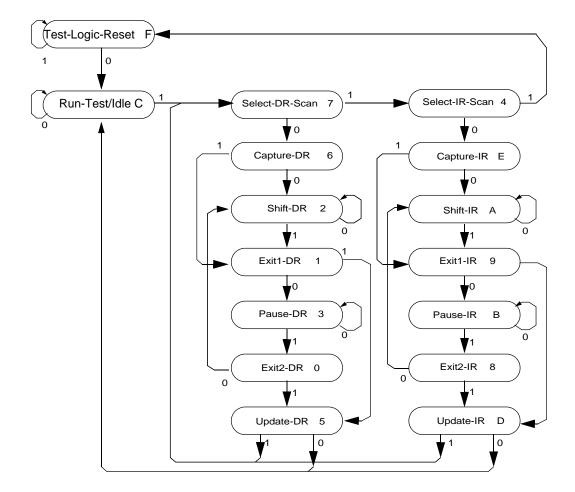

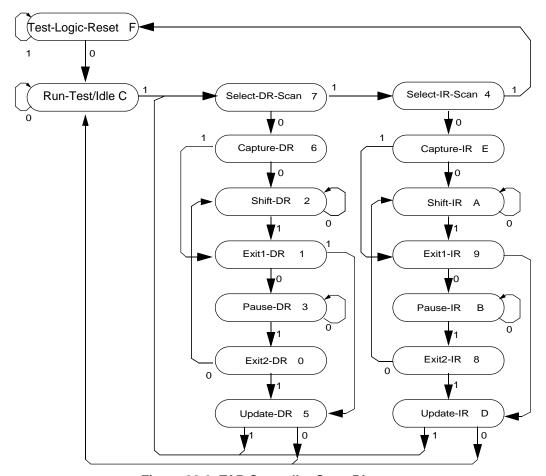

| 20.5 | TAP Controller                 | 20-4 |

|      | 20.5.1 Operation               | 20-6 |

| 20.6 | Memory Map                     | 20-9 |

| 20.7 | Pin Description                | 20-9 |

| 20.8 | Clocks                         | 20-9 |

|      | 20.8.1 TCK                     | 20-9 |

| 20.9 | Interrupts                     | 20-9 |

xiv Freescale Semiconductor

## Chapter 1 Device Overview

#### 1.1 The MC56F8006 Series

#### 1.1.1 Introduction

The 56F8006/56F8002 is a member of the 56800E core-based family of digital signal controllers (DSCs). It combines, on a single chip, the processing power of a DSP and the functionality of a microcontroller with a flexible set of peripherals to create an extremely cost-effective solution. Because of its low cost, configuration flexibility, and compact program code, the 56F8006/56F8002 is well-suited for many applications. The 56F8006/56F8002 includes many peripherals that are especially useful for cost-sensitive applications, including:

- Industrial control

- Home appliances

- Smart sensors

- Fire and security systems

- Switched-mode power supply and power management

- Power metering

- Motor control (ACIM, BLDC, PMSM, SR, and stepper)

- Handheld power tools

- Arc detection

- Medical device/equipment

- Instrumentation

- Lighting ballast

The 56800E core is based on a dual Harvard-style architecture consisting of three execution units operating in parallel, allowing as many as six operations per instruction cycle. The MCU-style programming model and optimized instruction set allow straightforward generation of efficient, compact DSP and control code. The instruction set is also highly efficient for C compilers to enable rapid development of optimized control applications.

The 56F8006/56F8002 supports program execution from internal memories. Two data operands can be accessed from the on-chip data RAM per instruction cycle. The 56F8006/56F8002 also offers up to 40 general-purpose input/output (GPIO) lines, depending on peripheral configuration.

Freescale Semiconductor

#### **NOTE**

In this manual, a reference to a register name such as PWM\_VAL*n* means that there are multiple related registers named PWM\_VAL1, PWM\_VAL2, etc.

### 1.1.2 MC56F8006 Series Device Comparison

This table compares the devices in the MC56F8006 series. The pinout configuration in these devices is highly multiplexed – each signal pin can be programmed to perform one of several functions. See the data sheet for details.

Table 1. MC56F8006 Series Device Comparison

| Factions                                         |        | MC56F8006 |        |        |  |

|--------------------------------------------------|--------|-----------|--------|--------|--|

| Feature                                          | 28-pin | 32-pin    | 48-pin | 28-pin |  |

| Flash memory size (Kbytes)                       |        | 16        | l      | 12     |  |

| RAM size (Kbytes)                                | 2      |           | •      |        |  |

| Analog comparators (ACMP)                        |        | ,         | 3      |        |  |

| Analog-to-digital converters (ADC)               |        |           | 2      |        |  |

| Unshielded ADC inputs                            | 6      | 7         | 7      | 6      |  |

| Shielded ADC inputs                              | 9      | 11        | 17     | 9      |  |

| Total number of ADC input pins <sup>1</sup>      | 15     | 18        | 24     | 15     |  |

| Programmable gain amplifiers (PGA)               |        | 2         |        |        |  |

| Pulse-width modulator (PWM) outputs              | 6      |           |        |        |  |

| PWM fault inputs                                 | 3      | 4         | 4      | 3      |  |

| Inter-integrated circuit (IIC)                   | 1      |           |        |        |  |

| Serial peripheral interface (SPI)                | 1      |           |        |        |  |

| High speed serial communications interface (SCI) | 1      |           |        |        |  |

| Programmable interrupt timer (PIT)               | 1      |           |        |        |  |

| Programmable delay block (PDB)                   | 1      |           |        |        |  |

| 16-bit multi-purpose timers (TMR)                | 2      |           |        |        |  |

| Real-time counter (RTC)                          | 1      |           |        |        |  |

| Computer operating properly (COP) timer          | Yes    |           |        |        |  |

| Phase-locked loop (PLL)                          | Yes    |           |        |        |  |

| 1 kHz on-chip oscillator                         | Yes    |           |        |        |  |

| 8 MHz (400 kHz at standby mode) on-chip ROSC     | Yes    |           |        |        |  |

Table 1. MC56F8006 Series Device Comparison

| Feature                                                                                | MC56F8006 |        |        | MC56F8002 |

|----------------------------------------------------------------------------------------|-----------|--------|--------|-----------|

| reature                                                                                | 28-pin    | 32-pin | 48-pin | 28-pin    |

| Crystal oscillator                                                                     | Yes       |        |        |           |

| Power management controller (PMC)                                                      | Yes       |        |        |           |

| IEEE 1149.1 Joint Test Action Group (JTAG) interface                                   | Yes       |        |        |           |

| Enhanced on-chip emulator (EOnCE) IEEE 1149.1 Joint Test Action Group (JTAG) interface | Yes       |        |        |           |

<sup>1</sup> Some ADC inputs share the same pin.

## 1.2 MC56F8006 Series Block Diagram

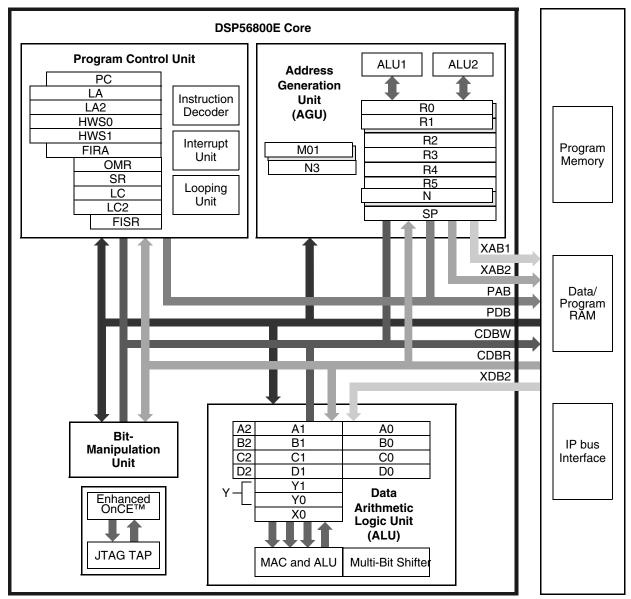

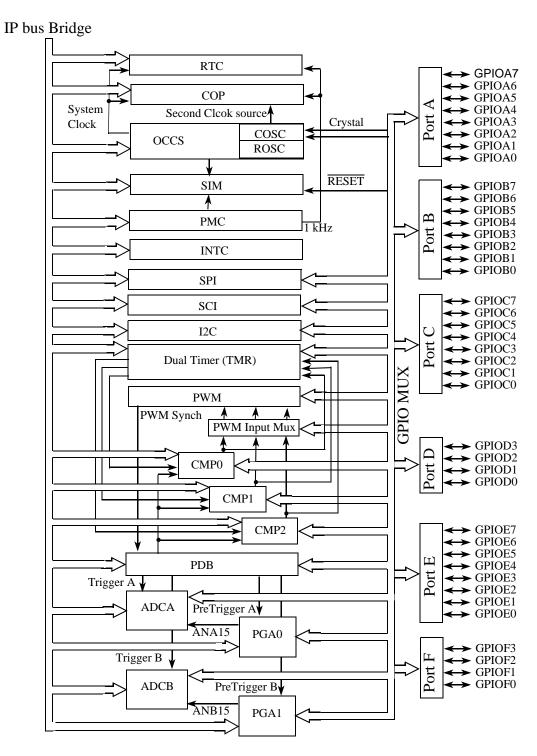

Figure 1-1 shows block diagrams of the 56800E system buses, their communication with internal memories and the IP bus interface, and the internal connections to each unit of the 56800E core. Figure 1-2 shows the peripherals and control blocks connected to the IP bus bridge.

Freescale Semiconductor 1-3

Figure 1-1. 56800E Core Block Diagram

Figure 1-2. Peripheral Subsystem

Freescale Semiconductor 1-5

## 1.3 High Performance Core

- Efficient 16-bit 56800E family Digital Signal Controller (DSC) engine with dual Harvard architecture

- Up to 32 Million Instructions Per Second (MIPS) at 32 MHz core frequency

- 155 Basic Instructions in conjunction with up to 20 address modes

- Single-cycle 16 × 16-bit parallel Multiplier-Accumulator (MAC)

- Four 36-bit accumulators, including extension bits

- 32-bit arithmetic and logic multi-bit shifter

- Parallel instruction set with unique DSP addressing modes

- Hardware DO and REP loops

- Three internal address buses

- Four internal data buses

- Instruction set supports both DSP and controller functions

- Controller-style addressing modes and instructions for compact code

- Efficient C compiler and local variable support

- Software subroutine and interrupt stack with depth limited only by memory

- JTAG/Enhanced On-Chip Emulation (OnCE) for unobtrusive, processor speed-independent, real-time debugging

### 1.4 Operation Range

- From power-on-reset: Approximately 1.9 V to 3.6 V

- Operating: 1.8 V to 3.6 V (power supplies and input/output)

- Ambient temperature operating range: -40 °C to 105 °C

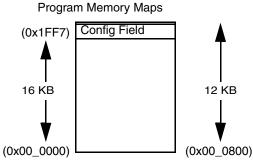

### 1.5 Memory Configuration

- Up to 16 Kbytes program flash memory with flash security protection

- 2 Kbytes unified program/data RAM

## 1.6 Module Configuration

- One 6-channel PWM module

- Up to 96 MHz PWM operating clock

- 15 bits of resolution

- Center-Aligned and edge-aligned PWM signal mode

- Four programmable fault inputs with programmable digital filter

- Double-Buffered PWM registers

- Each complementary PWM signal pair allows selection of a PWM supply source from:

- PWM generator

1-6 Freescale Semiconductor

- Internal timers

- Analog comparator outputs

- Two independent 12-bit analog-to-digital converters (ADCs)

- 3.042 μs for first 10- or 12-bit ADC conversion

- 2.5 μs for subsequent 10- or 12-bit ADC conversions

- Up to 28 analog inputs (internal and external) per ADC

- Output formatted in 12-, 10-, or 8-bit right-justified unsigned format

- Single or continuous conversion (automatic return to idle after single conversion)

- Configurable sample time and conversion speed/power

- Conversion complete flag and interrupt

- Input clock selectable from up to four sources

- Operation in wait or stop modes for lower noise operation

- Asynchronous clock source for lower noise operation

- Can be configured to take two samples (with no software reconfiguration required) based on hardware triggers during ping-pong mode

- Support simultaneous and software-triggering conversions

- Automatic compare with interrupt for less-than, or greater-than or equal-to, programmable value

- Temperature sensor

- Two differential programmable gain amplifiers (PGA)

- Sampled PGA architecture

- Common mode noise and offset are automatically cancelled out (2–4 consecutive samples required for noise/offset cancellation)

- Sample is able to be synchronized with PWM operation by using the PWM sync output and programmable delay block

- Sampling time can be precisely controlled (to less than 0.1 μs)

- Several programmable gains  $(1\times, 2\times, 4\times, 8\times, 16\times, \text{ and } 32\times)$

- 0.14 MSPS maximum

- Selectable tradeoff for slower/low power versus faster/more power

- Rail-to-rail input voltage range

- Single-ended output routed directly to on-chip ADCs ANA15 and ANB15

- Available software and hardware triggers

- Includes additional calibration features:

- Offset calibration eliminates any errors in the internal reference used to generate the VDDA/2 output center point

- Gain calibration can be used to verify the gain of the overall data path

- Both features require software correction of the ADC result

- One high-speed serial communication interface (SCI) with LIN slave functionality

Freescale Semiconductor 1-7

#### **Device Overview**

- Max baud rate of 6 Mbit/s when using 3× system clock at up to 96 MHz.

- Full-duplex or single-wire operation

- Two receiver wake-up methods:

- Idle line

- Address mark

- One serial peripheral interface (SPI)

- Full-duplex operation

- Master and slave modes

- Programmable Length Transactions (2 to 16 bits)

- Programmable transmit and receive shift order (MSB as first or last bit transmitted)

- Maximum slave module frequency = module clock frequency/2

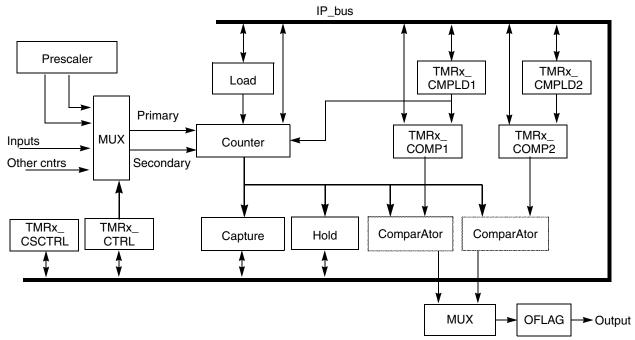

- One dual-channel 16-bit multi-purpose timer module (TMR)

- Up to 96 MHz operating clock

- Two independent 16-bit counter/timers with cascading capability

- Each timer has capture and compare capability

- Up to 12 operating modes

- Four external inputs and two external outputs

- One programmable interval timer (PIT)

- 16-bit counter with programmable counter modulo

- Interrupt capability

- Real-time counter (RTC) which can be used to implement a real-time clock

- 8-Bit up-counter

- Three software-selectable clock sources for input to prescaler with selectable binary-based and decimal-based divider values

- 1 kHz internal low-power oscillator

- External crystal oscillator/external clock source

- System bus (IPBus up to 32 MHz)

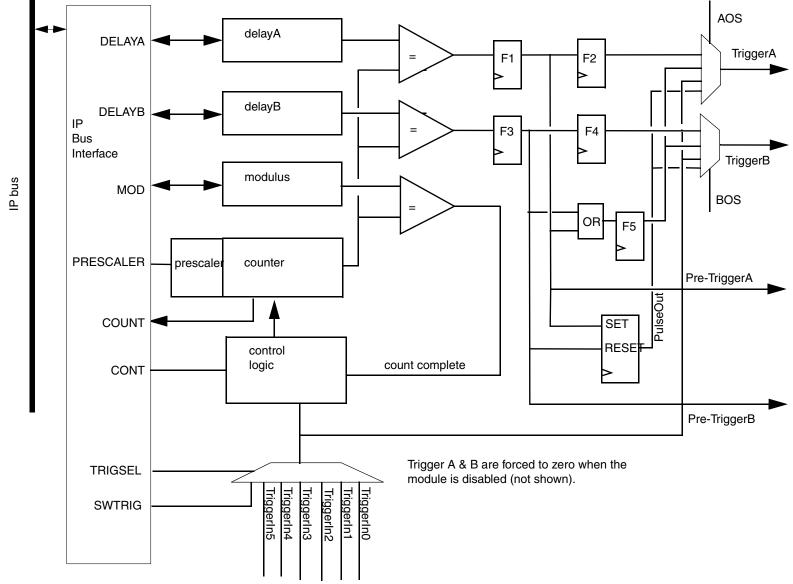

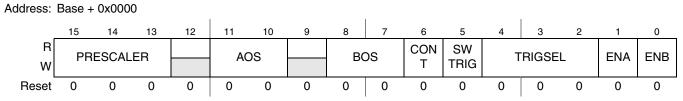

- One 16-bit programmable delay block (PDB)

- 16-bit counter with programmable counter modulo and delay time

- Counter is initiated by positive transition of internal or external trigger pulse

- Supports two independently controlled delay pulses used to synchronize PGA and ADC conversions with input

- trigger event

- Two PDB outputs can be ORed together to schedule two conversions from one input trigger event

- PDB outputs can be used to schedule precise edge placement for a pulsed output that generates the control signal for the CMP windowing comparison

- Supports continuous or single-shot mode

1-8 Freescale Semiconductor

- Supports Bypass mode

- One inter-integrated circuit (I<sup>2</sup>C) port

- Operates up to 400 kbps

- Supports both master and slave operation

- Supports both 10-bit address mode and broadcasting mode

- Supports System Management Bus (SMBus) version 2

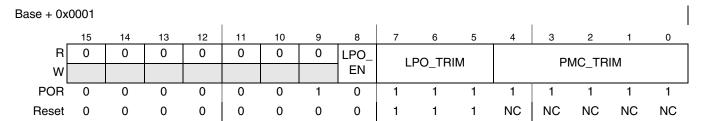

- Computer operating properly (COP)/watchdog timer capable of selecting different clock sources

- Programmable prescaler and timeout period

- Programmable wait, stop, and partial power-down mode operation

- Causes a loss of reference reset 128 cycles after a loss of the reference clock to the PLL is detected

- Choice of clock sources from four sources in support of EN60730 and IEC61508:

- On-chip relaxation oscillator

- External crystal oscillator/external clock source

- System clock (IPBus)

- On-chip low-power 1 kHz oscillator

- Clock sources

- On-chip 8 MHz relaxation oscillator

- On-chip 1 kHz clock

- External clock (32 kHz or 8 MHz): crystal oscillator, ceramic resonator, and external clock source

- Phase lock loop (PLL) provides a high-speed clock to the core and peripherals

- Provides 3x system clock to PWM, dual timer, and SCI

- Loss of lock interrupt

- Loss of reference clock interrupt

- Three analog comparators (CMPs)

- Selectable input source includes external pins, internal DACs

- Programmable output polarity

- Output can drive timer input, PWM fault input, PWM source, external pin output, and trigger ADCs

- Output falling- and rising-edge detection able to generate interrupts

- Up to 40 general-purpose I/O (GPIO) pins

- Individual setting of each pin in peripheral or GPIO mode

- Individual input/output direction control for each pin in GPIO mode

- Hysteresis and configurable pullup device on all input pins

- Configurable slew rate and drive strength and optional input low-pass filters on all output pins

- 20 mA sink/source current

- Power management controller (PMC)

Freescale Semiconductor

#### **Device Overview**

- On-chip regulator for digital and analog circuitry to lower cost and reduce noise

- Integrated power-on reset (POR)

- Low-voltage interrupt with a user-selectable trip voltage of 1.81 V or 2.31 V

- Selectable brown-out reset

- RUN, WAIT, and STOP modes

- Low-power RUN, WAIT, and STOP modes

- Partial Power Down mode

- RAM, PMC, and COP remain powered

- Rest of the chip is shut down for extreme power savings

- Each peripheral can be individually disabled to save power

- Integrated 1 kHz oscillator

- JTAG/EOnCE debug programming interface for real-time debugging

- IEEE 1149.1 Joint Test Action Group (JTAG) interface

- EOnCE interface for real-time debugging

### 1.7 System Clock Generation and Distribution

#### 1.7.1 Clock Generation

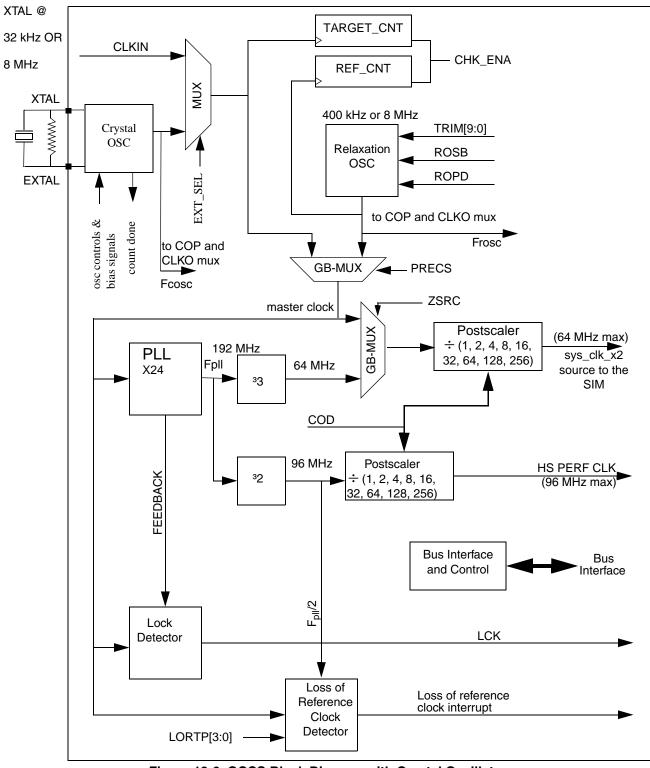

The MC56F8006 has numerous options for clock generation:

- On-chip relaxation oscillator (ROSC). This module nominally generates an 8 MHz clock signal. It is also capable of operating at 400 kHz when the device is in low-power mode.

- Very low power (VLP) crystal oscillator (COSC). This VLP module is designed for use with a 32 kHz crystal (low range mode), or a crystal or resonator in the 1 to 16 MHz range (high range mode). When used with the on-chip PLL, the maximum crystal/resonator frequency is 10 MHz.

- Off-chip external oscillator.

- 1 kHz low-power oscillator. This clock may be used by the COP module to wake the device from partial power down mode.

- Asynchronous ADC clock sources. There are two, one for each ADC hard block. They may be used to schedule ADC conversions asynchronously from the system clocks to reduce noise.

- The JTAG port is clocked asynchronously from the rest of the chip using the TCK signal supplied from off-chip.

#### 1.7.2 Clock Distribution

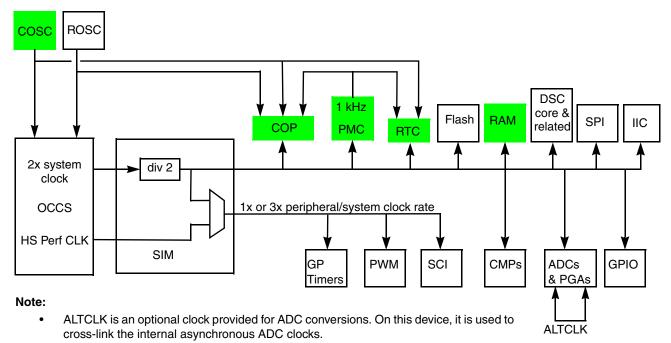

Figure 1-3 illustrates how the various clock frequencies are used on the device.

MC56F8006 Reference Manual, Rev. 0

- All peripheral clocks can be individually gated off within the SIM

- The COSC, COP, PMC and RTC all continue to operate in partial power down mode. Both COP and RTC can signal the PMC to exit PPD mode.

Figure 1-3. System Clock Distribution Diagram

The external oscillator, COSC, and ROSC can all be used as the PLL reference clock to generate 2x system clock. This signal runs at 2× the DSC core frequency. It is divided by two within the SIM to ensure a 50% duty cycle for clocks distributed across the chip. The external oscillator, COSC, and ROSC can also be used as 2x system clock directly.

## 1.7.3 Communication Between Peripherals

Peripherals are optimized for specific applications, and in many cases, their integration on-chip is optimized as well. This section outlines the communication between various peripherals on this device.

The two general-purpose timers can access the outputs of the three comparators (CMP0\_OUT, CMP1\_OUT, and CMP2\_OUT) as T0, T1, and TIN2 respectively. The muxing is controlled via the peripheral pin enable registers in the SIM. T0 and T1 timer pins can operate as either timer input or output pins. TIN2 and TIN3 are input pins only.

The HSCMP WINDOW/SAMPLE input can be supplied from PDB TriggerA/B or Timer 0/1 outputs. Muxing is controlled via internal peripheral select registers in the SIM.

The SCI, SPI, IIC are stand alone communications peripherals and do not communicate with other blocks on chip.

Each ADC contains a temperature sensor. Outputs of temperature sensors, PGAs, on-chip regulators, and VDDA are internally routed to the ADC inputs.

• Internal PGA0 output is available on ANA15

Freescale Semiconductor 1-11

#### **Device Overview**

- Internal PGA0 positive input calibration voltage is available on ANA16

- Internal PGA0 negative input calibration voltage is available on ANA17

- Internal PGA1 output is available on ANB15

- Internal PGA1 positive input calibration voltage is available on ANB16

- Internal PGA1 negative input calibration voltage is available on ANB17

- ADCA temperature sensor is available on ANA26

- ADCB temperature sensor is available on ANB26

- Output of on-chip digital voltage regulator is routed to ANA24 and ANB24

- Output of on-chip analog voltage regulator is routed to ANA25 and ANB25

- VDDA is routed to ANA27 and ANB27

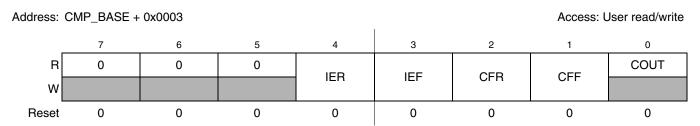

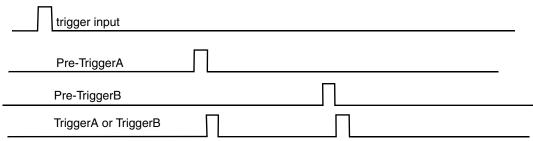

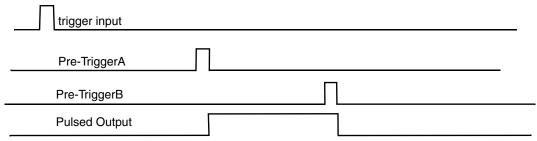

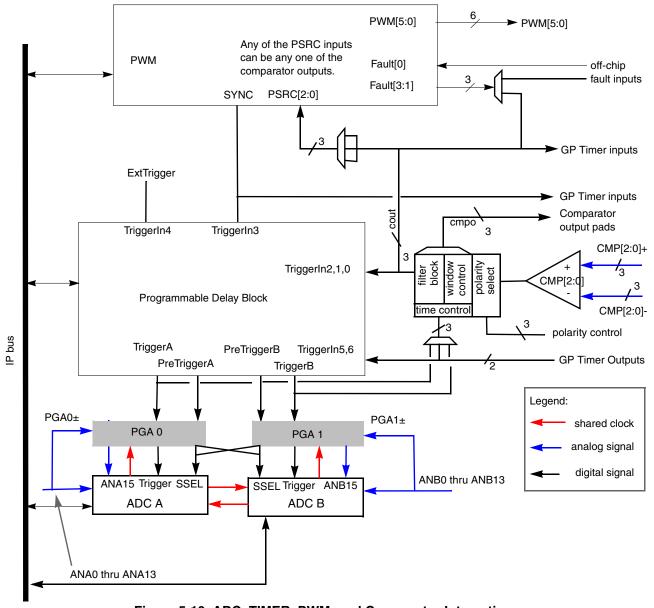

The comparators, timers, and PWM\_reload\_sync output can be connected to the programmable delay block (PDB) trigger input. The PDB pre-trigger A and trigger A outputs are connected to the ADCA and PGA0 hardware trigger inputs. The PDB pre-trigger B and trigger B outputs are connected to the ADCB and PGA1 hardware trigger inputs. When the input trigger of PDB is asserted, PDB trigger and pre-trigger outputs are asserted after a delay of a pre-programmed period.

1-12 Freescale Semiconductor

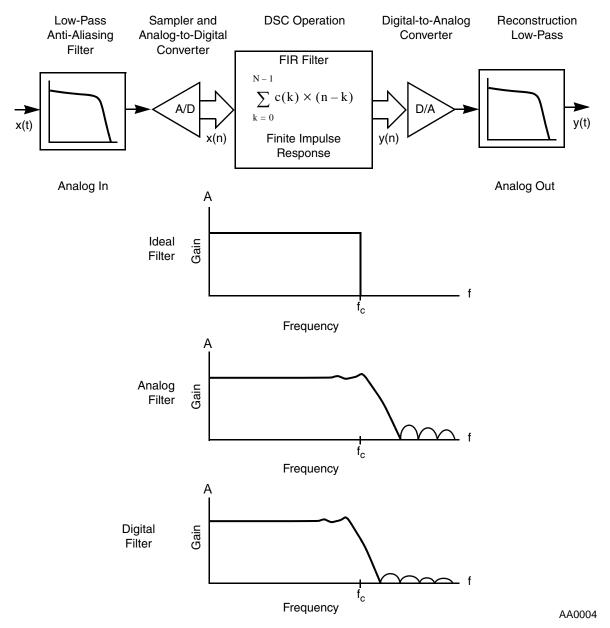

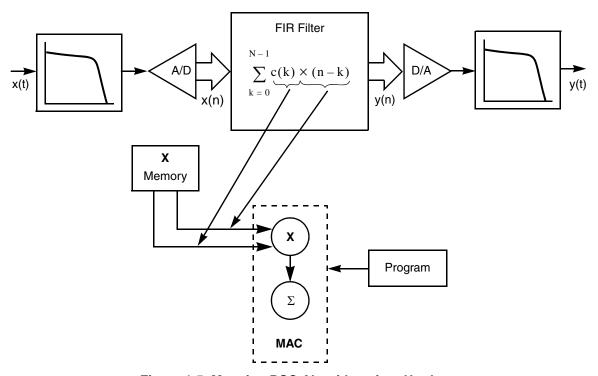

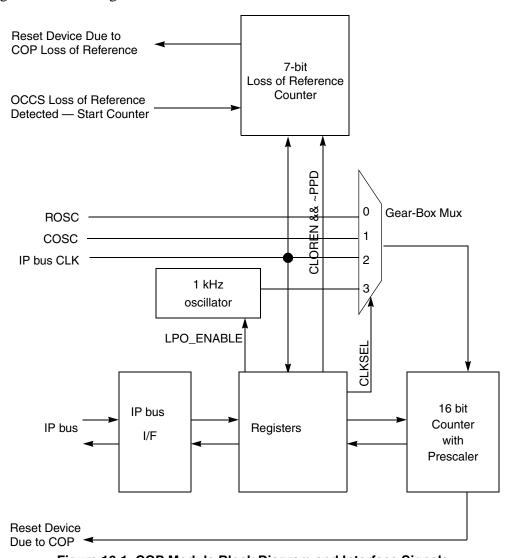

Figure 1-4. Digital Signal Processing

Processing in this circuit begins by band-limiting the input signal with an anti-alias filter, eliminating out-of-band signals that can be aliased back into the pass band due to the sampling process. The signal is then sampled, digitized with an ADC, and sent to the DSC. The filter implemented by the DSC is strictly a matter of software. The DSC can directly employ any filter that can also be implemented using analog techniques. Also, adaptive filters can be easily put into practice using DSC, whereas these filters are extremely difficult to implement using analog techniques. Similarly, compression can also be implemented on a DSC. The DSC output is processed by a DAC and is low-pass filtered to remove the effects of digitizing.

Freescale Semiconductor 1-13

#### 1.7.4 **Key DSC Attributes**

The key attributes of a DSC are:

- Multiply-accumulate (MAC) operations sustained at one cycle per MAC, including memory accesses

- Fetching up to two operands per instruction cycle for the MAC

- Program control to provide versatile operation and zero overhead looping

- Input/output to move data in and out of the DSC

These are shown schematically in Figure 1-5.

Figure 1-5. Mapping DSC Algorithms into Hardware

The multiply-accumulation (MAC) operation is the fundamental operation used in DSP. The core of the MC56F8006 series has a dual Harvard architecture optimized for MAC operations. The two operands shown in Figure 1-5, c() and x(), are directed to a multiply operation, and the result is summed. This process is built into the chip by allowing two separate data-memory accesses to feed a single-cycle MAC. The entire process must occur under program control to direct the correct operands to the multiplier and save the accumulated result as needed. Because the memory and the MAC are independent, the DSC can perform two memory moves, a multiply and an accumulate, and two address updates in a single operation cycle. As a result, DSP and MCU benchmarks execute very efficiently.

#### 1.7.5 Advantages of DSC

The advantages of using the DSC include the following:

Fewer components

MC56F8006 Reference Manual, Rev. 0

- Stable, deterministic performance

- No analog filter adjustments

- Wide range of applications

- Filters with much closer tolerances

- High noise immunity

- Adaptive filters easily implemented

- Self-test can be built in

- Better power-supply rejection

Freescale Semiconductor 1-15

**Device Overview**

1-16 Freescale Semiconductor

## Chapter 2 Analog-to-Digital Converter (ADC)

#### 2.1 Introduction

The 12-bit analog-to-digital converter (ADC) is designed for operation with a DSC.

#### 2.1.1 Features

Features of the ADC module include:

- Input voltage values may range from V<sub>SSA</sub> to V<sub>DDA</sub>.

- Up to 28 analog inputs.

- Output formatted in 12-, 10- or 8-bit right-justified format.

- Single or continuous conversion (automatic return to idle after single conversion).

- Configurable sample time and conversion speed/power.

- Conversion complete flag and interrupt.

- Input clock selectable from up to four sources.

- Operation in wait or stop modes for lower noise operation.

- Asynchronous clock source for lower noise operation.

- Support of simultaneous and software triggering conversions.

- Temperature sensors that are routed to ANA26 and ANB26.

- Can be configured to take two samples (with no software reconfiguration required) based on hardware triggers during ping-pong mode.

#### 2.1.2 Related Material

This block interfaces directly with the programmable gain amplifier and programmable delay block. See Chapter 5, "Programmable Delay Block (PDB)," for additional information.

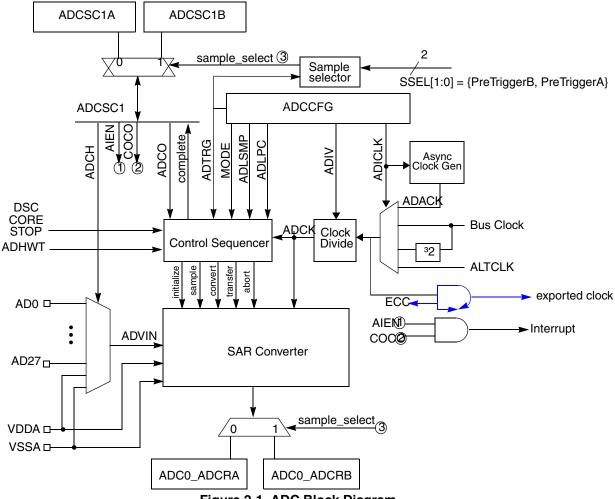

## 2.1.3 Block Diagram

Figure 2-1 provides a block diagram of the ADC module.

Figure 2-1. ADC Block Diagram

## 2.2 External Signal Description

The ADC module supports up to 28 separate analog inputs.

Table 2-1. Signal Properties

| Name     | Function              |

|----------|-----------------------|

| AD27–AD0 | Analog Channel inputs |

## 2.2.1 Analog Channel Inputs (ADn)

The ADC module supports up to 28 separate analog inputs. An input is selected for conversion through the ADCH channel select bits.

### 2.3 Register Definition

Memory mapped registers shown in Table 2-2 control and monitor operation of the ADC.

**Address Register Name** Description Offset ADC0\_ADCSC1A 0x0Status and control register 1A Status and control register ADC0 ADCSC2 0x1Reserved 0x2 Reserved 0x3 Reserved 0x4 Reserved 0x5 ADC0\_ADCCFG Configuration register 0x6 Reserved 0x7 Reserved 0x8 Reserved 0x9 ADC0\_ADCSC1B Status and control register 1B 0xA ADC0 ADCRA Data result register A 0xB ADC0\_ADCRB 0xC Data result register B Reserved 0xD Reserved 0xE

**Table 2-2. ADC Registers**

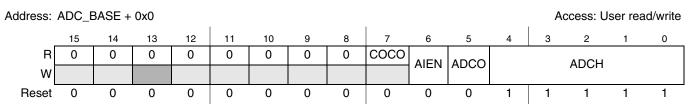

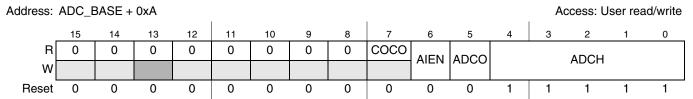

## 2.3.1 Status and Control Register 1A and 1B (ADC0\_ADCSC1A and ADC0\_ADCSC1B)

This section describes the function of the ADC status and control registers, ADC0\_ADCSC1A and ADC0\_ADCSC1B. These registers have identical fields, and are used in a "ping-pong" approach to control ADC operation. At any one point in time, only one of ADC0\_ADCSC1A and ADC0\_ADCSC1B is actively controlling the ADC analog core. It is possible to write to ADC0\_ADCSC1A while ADC0\_ADCSC1B is driving a conversion, and vice-versa. Writing ADC0\_ADCSC1A while it is actively controlling a conversion aborts the current conversion and initiates a new conversion (if the ADCH bits are equal to a value other than all 1s). The same applies to ADC0\_ADCSC1B.

Figure 2-2. Status and Control Register 1A (ADC0\_ADCSC1A)

Freescale Semiconductor 2-3

Figure 2-3. Status and Control Register 1B (ADC0\_ADCSC1B)

Table 2-3. ADC0\_ADCSC1A/B Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15–8        | Reserved. Read and write as zero                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 7<br>COCO   | Conversion Complete Flag. The COCO flag is a read-only bit that is set each time a conversion is completed when the compare function is disabled (ACFE = 0). When the compare function is enabled (ACFE = 1) the COCO flag is set upon completion of a conversion only if the compare result is true. This bit is cleared whenever ADCSC1 is written or whenever ADCRL is read.  0 Conversion not completed 1 Conversion completed                                                                                                                                                                                                                                                                                           |

| 6<br>AIEN   | Interrupt Enable. AIEN is used to enable conversion complete interrupts. When COCO becomes set while AIEN is high, an interrupt is asserted.  O Conversion complete interrupt disabled  Conversion complete interrupt enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5<br>ADCO   | Continuous Conversion Enable. ADCO is used to enable continuous conversions.  O One conversion following a write to the ADCSC1 when software triggered operation is selected, or one conversion following assertion of ADHWT when hardware triggered operation is selected.  Continuous conversions initiated following a write to ADCSC1 when software triggered operation is selected. Continuous conversions are initiated by an ADHWT event when hardware triggered operation is selected.                                                                                                                                                                                                                               |

| 4–0<br>ADCH | Input Channel Select. The ADCH bits form a 5-bit field that is used to select one of the input channels. The input channels are detailed in Figure 2-4.  The analog-to-digital converter subsystem is turned off when the channel select bits are all set to 1. This feature allows for explicit disabling of the ADC and isolation of the input channel from all sources. Terminating continuous conversions this way prevents an additional, single conversion from being performed. It is not necessary to set the channel select bits to all 1s to place the ADC in a low-power state when continuous conversions are not enabled because the module automatically enters a low-power state when a conversion completes. |

**Table 2-4. Input Channel Select**

| ADCH  | Input Select |

|-------|--------------|

| 00000 | AD0          |

| 00001 | AD1          |

| 00010 | AD2          |

| 00011 | AD3          |

| 00100 | AD4          |

| 00101 | AD5          |

| 00110 | AD6          |

| ADCH  | Input Select |

|-------|--------------|

| 10000 | AD16         |

| 10001 | AD17         |

| 10010 | AD18         |

| 10011 | AD19         |

| 10100 | AD20         |

| 10101 | AD21         |

| 10110 | AD22         |

2-4 Freescale Semiconductor

| ADCH  | Input Select |

|-------|--------------|

| 00111 | AD7          |

| 01000 | AD8          |

| 01001 | AD9          |

| 01010 | AD10         |

| 01011 | AD11         |

| 01100 | AD12         |

| 01101 | AD13         |

| 01110 | AD14         |

| 01111 | AD15         |

| ADCH  | Input Select      |

|-------|-------------------|

| 10111 | AD23              |

| 11000 | AD24              |

| 11001 | AD25              |

| 11010 | AD26              |

| 11011 | AD27              |

| 11100 | Reserved          |

| 11101 | V <sub>REFH</sub> |

| 11110 | V <sub>REFL</sub> |

| 11111 | Module disabled   |

## 2.3.2 Status and Control Register 2 (ADC0\_ADCSC2)

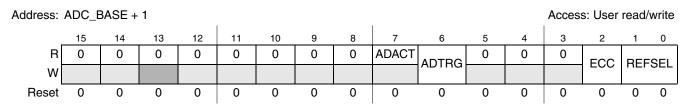

The ADC0\_ADCSC2 register is used to control the conversion trigger and conversion active of the ADC module

Figure 2-4. Status and Control Register 2 (ADC0\_ADCSC2)

Table 2-5. ADC0\_ADCSC2 Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15–0       | Reserved. Read and write as zero                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7<br>ADACT | Conversion Active. ADACT indicates that a conversion is in progress. ADACT is set when a conversion is initiated and cleared when a conversion is completed or aborted.  O Conversion not in progress  Conversion in progress                                                                                                                                                                                                                         |

| 6<br>ADTRG | Conversion Trigger Select. ADTRG is used to select the type of trigger to be used for initiating a conversion. Two types of trigger are selectable: software trigger and hardware trigger. When software trigger is selected, a conversion is initiated following a write to ADCSC1. When hardware trigger is selected, a conversion is initiated following the assertion of the ADHWT input.  O Software trigger selected  Hardware trigger selected |

Table 2-5. ADC0\_ADCSC2 Register Field Descriptions (continued)

| Field    | Description                                                                                                                                                                                                                                           |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5–3      | Reserved. Read and write as zero                                                                                                                                                                                                                      |

| 2<br>ECC | Enable Continuous Clock output. This bit gates the exported clock output of the ADC module. Set to zero to conserve power if the ADC clock output is not required by other on-chip devices.  Output clock is forced inactive  Output clock is enabled |

### 2.3.3 Data Result Registers A and B (ADC0\_ADCRA and ADC0\_ADCRB)

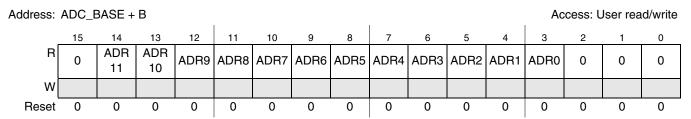

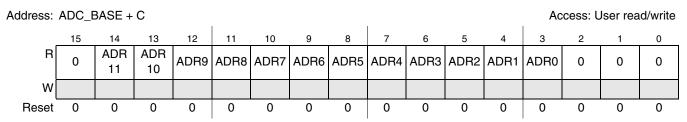

Figure 2-5. Data Result Register (ADC0\_ADCRA)

Figure 2-6. Data Result Register (ADC0 ADCRB)

In 12-bit operation, ADCR[14:3] contains the full 12-bit conversion result. In 10-bit mode, ADCR[12:3] contains the 10-bit conversion result and ADR[14:13] are both zero. Likewise, when configured for 8-bit mode, the result is in ADR[10:3] and ADR[14:11] are zero.

ADCR is updated each time a conversion completes.

In the case that the MODE bits are changed, any data in ADCR becomes invalid.

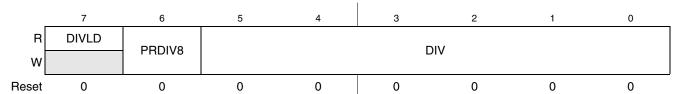

## 2.3.4 Configuration Register (ADC0\_ADCCFG)

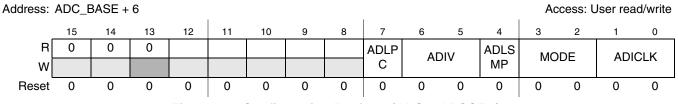

ADCCFG is used to select the mode of operation, clock source, clock divide, and configure for low power or long sample time.

Figure 2-7. Configuration Register (ADC0\_ADCCFG)

2-6 Freescale Semiconductor

#### MC56F8006 Reference Manual, Rev. 0

Table 2-6. ADC0\_ADCCFG Register Field Descriptions

| Field          | Description                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ADLPC     | Low Power Configuration. ADLPC controls the speed and power configuration of the analog-to-digital converter. This is used to optimize power consumption when higher sample rates are not required.  O High speed configuration  Low power configuration: The power is reduced at the expense of maximum clock speed.                                                                                                                     |

| 6, 5<br>ADIV   | Clock Divide Select. ADIV select the divide ratio used by the ADC to generate the internal clock ADCK. Table 2-7 shows the available clock configurations.                                                                                                                                                                                                                                                                                |

| 4<br>ADLSMP    | Long Sample Time Configuration. ADLSMP selects between long and short sample time. This adjusts the sample period to allow higher impedance inputs to be accurately sampled or to maximize conversion speed for lower impedance inputs. Longer sample times can also be used to lower overall power consumption when continuous conversions are enabled if high conversion rates are not required.  O Short sample time  Long sample time |

| 3, 2<br>MODE   | Conversion Mode Selection. MODE bits are used to select between 12-, 10- or 8-bit operation. See Table 2-8.                                                                                                                                                                                                                                                                                                                               |

| 1, 0<br>ADICLK | Input Clock Select. ADICLK bits select the input clock source to generate the internal clock ADCK. See Table 2-9.                                                                                                                                                                                                                                                                                                                         |

**Table 2-7. Clock Divide Select**

| ADIV | Divide Ratio | Clock Rate      |

|------|--------------|-----------------|

| 00   | 1            | Input clock     |

| 01   | 2            | Input clock ÷ 2 |

| 10   | 4            | Input clock ÷ 4 |

| 11   | 8            | Input clock ÷ 8 |

**Table 2-8. Conversion Modes**

| MODE | Mode Description         |

|------|--------------------------|

| 00   | 8-bit conversion (N=8)   |

| 01   | 12-bit conversion (N=12) |

| 10   | 10-bit conversion (N=10) |

| 11   | Reserved                 |

**Table 2-9. Input Clock Select**

| ADICLK | Selected Clock Source      |

|--------|----------------------------|

| 00     | Bus clock                  |

| 01     | Bus clock divided by 2     |

| 10     | Alternate clock (ALTCLK)   |

| 11     | Asynchronous clock (ADACK) |

#### MC56F8006 Reference Manual, Rev. 0

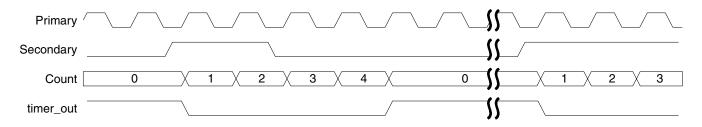

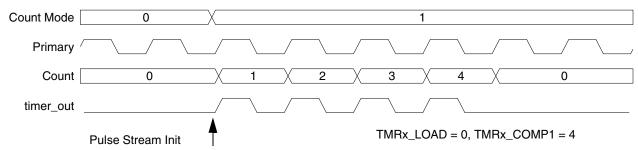

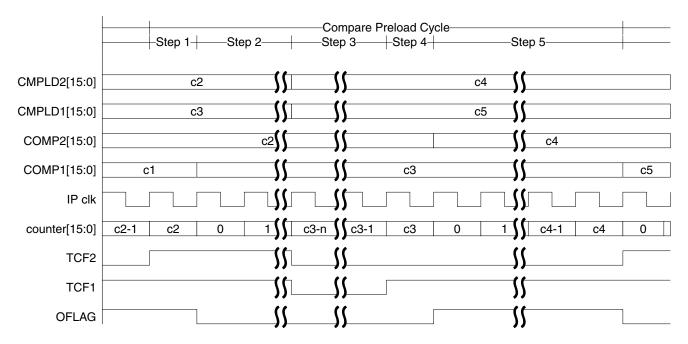

# 2.4 Functional Description